软件标签:Active-HDL 12

Active-HDL 12破解版是基于Windows的集成FPGA设计创建和仿真解决方案,用于基于团队的环境。 Active-HDL中的集成设计环境(IDE)包括完整的HDL和图形设计工具套件以及RTL /门级混合语言模拟器,用于快速部署和验证FPGA设计。设计流程管理器在设计输入,仿真,综合和实施流程中调用了200多种EDA和FPGA工具,并允许团队在整个FPGA开发过程中停留在一个通用平台内。 Active-HDL支持来自Intel(Altera),Lattice,Microsemi(Actel),Quicklogic,Xilinx等行业领先的FPGA设备。Active-HDL中的设计套件利用图形和文本设计输入方法,并将200多种EDA工具集成到一个平台中。 设计管理工具有助于消除FPGA开发过程中基于团队的设计所面临的问题。 Active-HDL将通用的内核混合语言模拟器与交互式工具结合在一起,使设计人员能够快速调试。 诸如Advanced Data Flow和Xtrace之类的调试工具为用户提供了系统内部信号的图形表示,从而提高了可观察性并有助于大型设计的调试。 Active-HDL还包括代码覆盖率和分析工具,使设计人员可以将度量驱动的验证纳入设计过程。 Active-HDL使设计人员能够快速记录其设计工作区的所有方面,以供以后查看,重用和归档。这样就可以在开发过程的所有阶段维护适当的文档,从而消除了多团队设计环境所面临的许多问题。 全新破解版下载,欢迎有需要的朋友来本站下载体验!

功能特色

2、项目管理

统一的基于团队的设计管理可保持本地或远程团队之间的一致性

可配置的FPGA/EDA Flow Manager与200多家供应商工具接口,使团队可以在整个FPGA开发过程中保持在一个平台上

3、图形/文字设计输入

通过使用文本,原理图和状态机快速部署设计

使用更安全,更可靠的互操作加密标准来分发或交付IP

4、仿真与调试

强大的通用内核混合语言模拟器,支持VHDL,Verilog,SystemVerilog和SystemC

使用图形交互调试和代码质量工具确保代码质量和可靠性

使用代码覆盖率分析工具执行指标驱动的验证,以识别设计中未执行的部分

使用ABV-基于断言的验证(SVA,PSL,OVA)提高验证质量并发现更多错误

能够模拟高级验证结构,例如SV功能覆盖率,约束随机化和UVM

使用MATLAB®/Simulink®接口连接HDL仿真与DSP模块的高级数学建模环境之间的差距

5、文档HTML/PDF

抽象设计智能,并使用HDL到原理图转换器以易于理解的图形形式表示它们

通过自动生成HTML和PDF设计文档快速共享设计

软件优势

1、设计输入和文档

DM Designer版PE EE

HDL,文本,框图和状态机编辑器

带有模板和自动完成的语言助手

宏,Tcl / Tk,Perl脚本支持

鼠标笔触

Code2Graphics™转换器

旧版原理图设计导入和符号导入/导出

导出为PDF / HTML /位图图形

2、项目管理

适用于所有FPGA供应商的设计流程管理器

版本控制界面

基于团队的设计管理

PCB接口

3、代码生成工具

IP核心组件生成器

从波形生成测试平台

从状态图生成测试平台

4、支持标准

VHDL IEEE 1076(1993、2002、2008和2018)

Verilog®HDL IEEE 1364(1995、2001和2005)

SystemVerilog IEEE 1800™-2012(设计)

EDIF 2 0 0

SystemC™2.3.1 IEEE 1666™/ TLM 2.0

SystemVerilog IEEE 1800™-2012(验证)

5、模拟/验证

仿真性能

(比FPGA供应商提供的模拟器快2倍的基准速度)

基准线

单一或混合语言设计支持仅混合仅混合

仿真模型保护/库加密

VHDL / Verilog IEEE兼容加密

增值转储(VCD和扩展VCD)支持

Verilog编程语言接口(PLI / VPI)

VHDL编程语言接口(VHPI)

批处理模式仿真/回归(VSimSA)

预编译的FPGA供应商库

Xilinx SecureIP支持

英特尔®中性库

Microsemi®语言中性库

探查器(性能指标)

SFM(服务器场管理器)

64位模拟

6、HDL调试和分析

交互式代码执行跟踪

高级断点管理

内存查看器

波形查看器

波形刺激器

波形比较和编辑

仿真后调试

C ++调试器

信号代理(仅限VHDL和混合信号)

X-Trace

高级数据流

与Riviera-PRO和ALINT-PRO选件集成

断言调试

7、断言和覆盖率工具

代码,语句,分支,表达式,条件,路径,切换范围和功能范围

PSL IEEE 1850,SystemVerilog IEEE 1800™,OpenVera断言

8、设计规则检查

带有Aldec基本规则库的ALINT™-PRO

DO-254 VHDL或Verilog规则库

STARC®VHDL或Verilog规则库

RMM Verilog和VHDL规则库

9、协同仿真

Simulink®协同仿真

MATLAB®协同仿真

10、支持平台

Windows®10 32/64位,Windows Server 2012、2016、2019 32/64位

安装激活教程

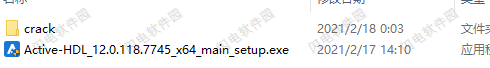

1、在本站下载并解压,如图所示

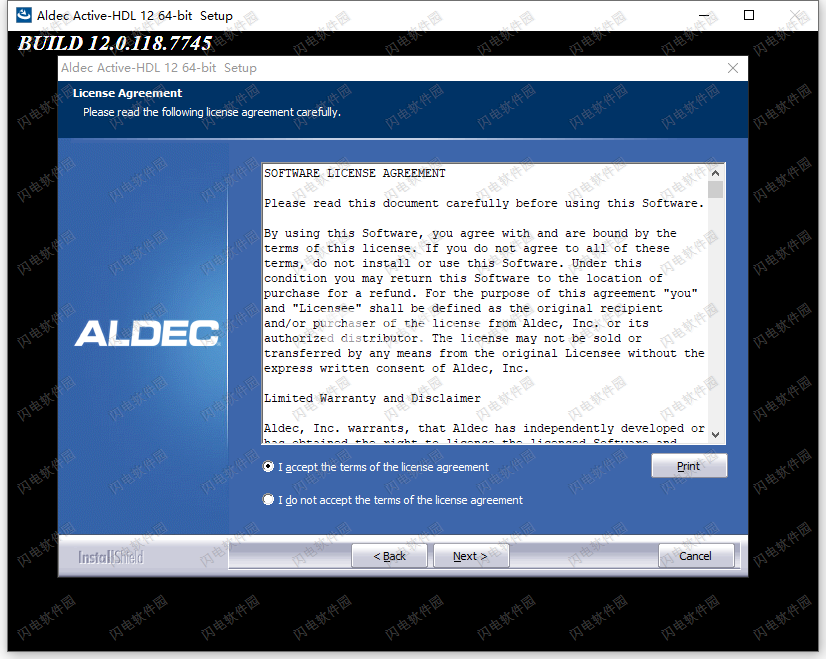

2、双击Active-HDL_12.0.118.7745_x64_main_setup.exe运行安装, 勾选我接受许可证协议条款

3、输入任意公司名

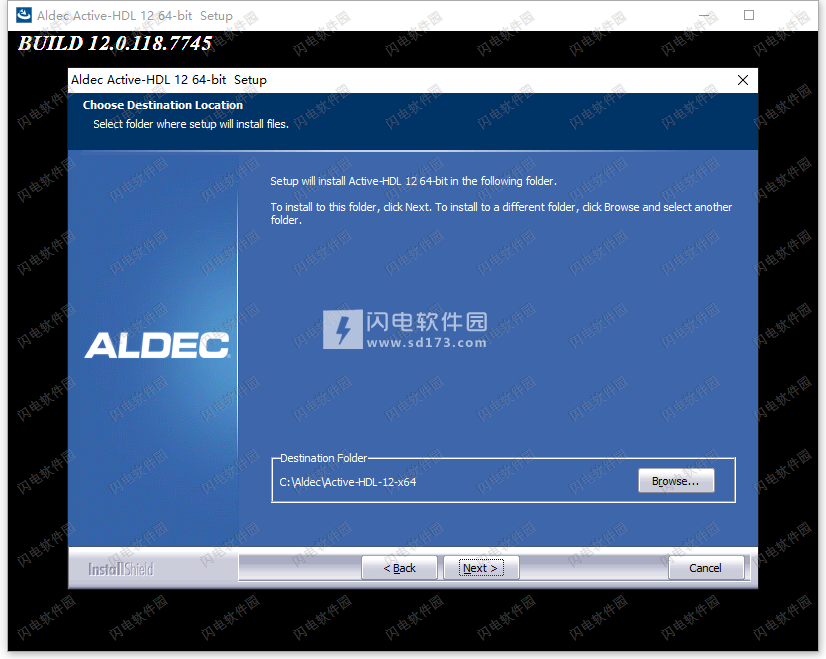

4、选择软件安装路径

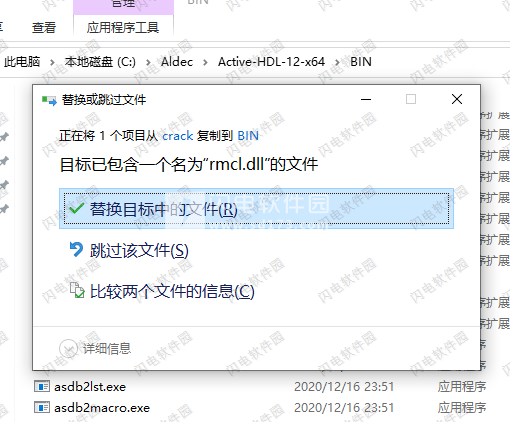

5、安装完成,将crack下的rmcl.dll文件复制到安装目录下的bin文件夹中,点击替换目标中的文件

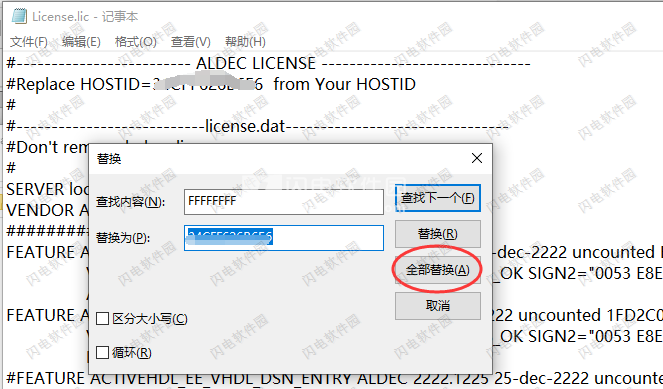

6、以记事本的方式打开license.lic,并使用您的MAC或以太网地址将hostid="FFFFFFFF"中的FFFFFFFF替换掉,使用编辑-替换,将所有的FFFFFFFF都替换掉,MAC或以太网地址不要带“-”,完成后保存(mac地址查询,使用win+r,输入cmd,然后在命令提示符窗口中输入ipconfig /all,点击回车即可)

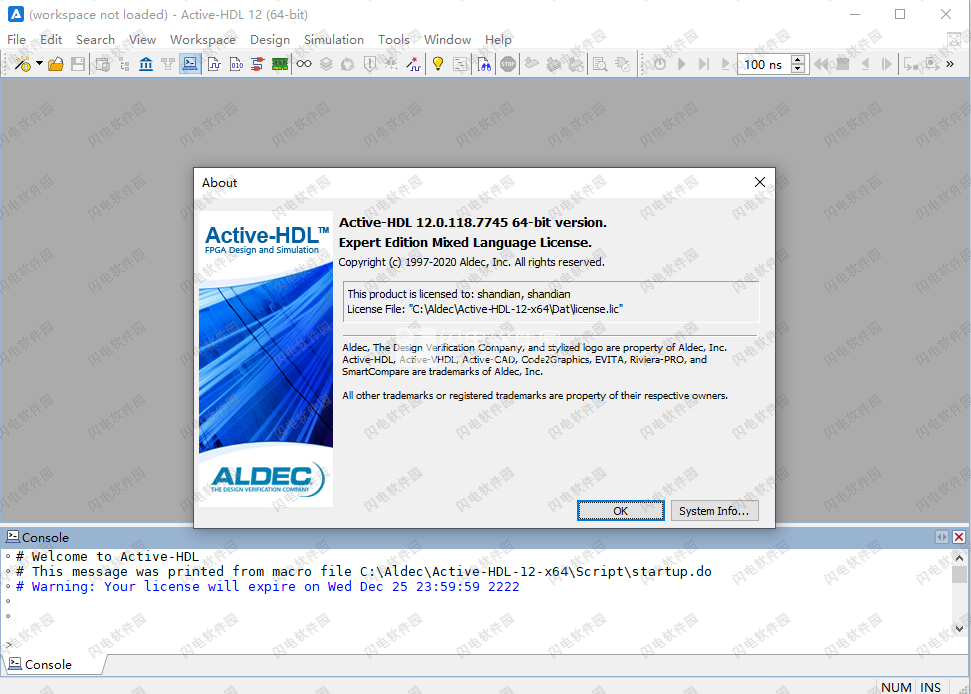

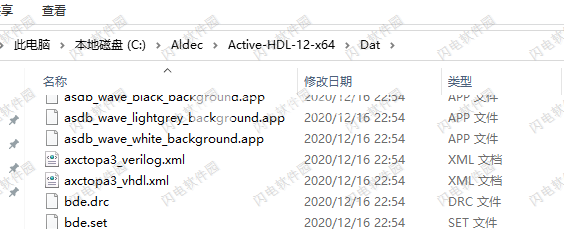

7、将修改后的License复制到安装目录中,例如默认C:\Aldec\Active-HDL 12 64-bit\Dat\license.lic

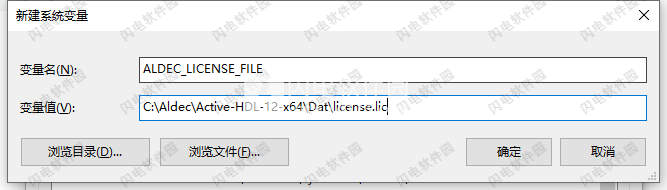

8、创建系统环境变量

变量名:ALDEC_LICENSE_FILE

变量值:license.lic路径,例如默认C:\Aldec\Active-HDL-12-x64\Dat\license.lic

9、完成后运行程序享用即可

闪电小编说明:

统一的基于团队的设计管理,可使用文本,原理图和状态机快速部署设计。功能强大的通用内核混合语言模拟器(VHDL,Verilog,SystemVerilog / UVM和SystemC),具有高级调试和代码覆盖率、基于声明的验证(SVA,PSL,OVA)、使用MATLAB®/Simulink®接口进行DSP协同仿真以及通过自动生成HTML和PDF格式的设计文档快速共享设计等功能优势

软件无法下载?不知道解压密码?微信关注订阅号"闪电下载"获取

本帖长期更新最新版 请收藏下载!版权声明:本站提的序列号、注册码、注册机、破解补丁等均来自互联网,仅供学习交流之用,请在下载后24小时内删除。