SynaptiCAD Product Suite 20ΤΤΫβΑφΫΪΈΣΒγΤχΙΛ≥Χ ΠΟ«ΩλΥΌ¥¥Ϋ®ΆξΟάΒΡ…ηΦΤΘ§Α≤ΉΑΆξ≥…ΑϋΚ§ΕύΗω Β”Ο≥Χ–ρΘ§Τδ÷–TestBencher¥ζ±μΝΥHDL≤β ‘ΤΫΧ®Ή‘Ε·Μ·ΩΣΖΔ÷–ΒΡ“Μœν÷Ί¥σΆΜΤΤΓΘ TestBencher ProΈΣ…ηΦΤ»Υ‘±ΧαΙ©ΝΥ”Ο”ΎΩλΥΌ…ζ≥…œΒΆ≥ΦΕ≤β ‘ΤΫΧ®ΒΡΆΦ–ΈΜΖΨ≥ΓΘ ”ΟΜßΜφ÷Τ ±–ρΆΦΘ§»ΜΚσTestBencher…ζ≥…±ΨΜζVHDLΘ§VerilogΘ§OpenVera.eΚΆC ++¥ζ¬κΓΘ …ζ≥…ΒΡ¥ζ¬κ «ΡΘΩιΜ·ΒΡΘ§Ω…“‘”κΥυ”–÷ς“ΣΒΡVHDLΚΆVerilogΡΘΡβΤς“ΜΤπ Ι”ΟΓΘVerilogger Pro «“Μ÷÷–¬–ΆVerilogΖ¬’φΜΖΨ≥Θ§ΫΪ¥ΪΆ≥VerilogΖ¬’φΤςΒΡΥυ”–ΙΠΡή”κΒΊ«ρ…œΉν«Ω¥σΒΡΆΦ–Έ≤β ‘ ΗΝΩ…ζ≥…ΤςΫαΚœ‘Ύ“ΜΤπΓΘ ‘ΎVerilogger Pro÷–Θ§ΡΘ–Ά≤β ‘ «»γ¥Υ÷°ΩλΘ§“‘÷Ν”ΎΡζΩ…“‘Ε‘…ηΦΤ÷–ΒΡΟΩΗωΡΘ–ΆΫχ––’φ’ΐΒΡΉ‘œ¬Εχ…œΒΡ≤β ‘Θ§Εχ’β‘Ύ –≥ΓΨΚ’υ÷–Ά®≥ΘΜα±ΜΧχΙΐΓΘ

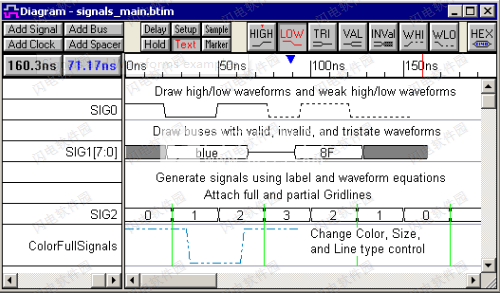

WaveFormer ProΆ®ΙΐΫΪ ±–ρΖ÷ΈωΚΆΫΜΜΞ ΫΖ¬’φœύΫαΚœΘ§Ω…“‘Αο÷ζΡζΗϋΩλΒΊ…ηΦΤΘ§Φθ…Ό¥μΈσΓΘ ΩλΥΌ δ»κ…ηΦΤΒΡΜυ±Ψ‘ΣΥΊΘ§ΕχΈό–η¥¥Ϋ®‘≠άμΆΦΜρHDLΡΘ–ΆΓΘ –όΗΡ…ηΦΤ ±Θ§Ω…“‘Φ¥ ±Ζ¥άΓΘ§¥”Εχ÷π≤ΫΫχ––Ζ¬’φΓΘ ¥” ±–ρΆΦ…ζ≥…VHDLΘ§VerilogΘ§SPICEΚΆ¬κ–Ά…ζ≥…Τς¥ζ¬κΓΘ ΒΦ»κ¥”¬ΏΦ≠Ζ÷Έω“«ΚΆVCDΈΡΦΰΜώ»ΓΒΡ≤®–Έ ΐΨίΓΘΡζΫΪ÷Μ–η“ΣΑ≤ΉΑ“Μ¥ΈΨΆ”Β”–Άξ’ϊΒΡΫβΨωΖΫΑΗΘ§≤Δ«“Α≤ΉΑΤΤΫβΖ«≥ΘΦρΒΞΘ§Α≤ΉΑΑϋ÷–Κ§–μΩ…Οή‘ΩΈΡΦΰΘ§Η¥÷ΤΒΫΑ≤ΉΑΡΩ¬Φ÷–Φ¥Ω…Άξ≥…ΤΤΫβΘΓ

»μΦΰΧΊ…Ϊ

1ΓΔ“‘ΆΦ–ΈΖΫ Ϋ…ζ≥…VHDLΘ§VerilogΚΆSPICE≤β ‘Χ®

WaveFormer ProΘ§”Ο”ΎΫω”Ο”Ύ¥ΧΦΛΒΡ≤β ‘Χ®

WaveFormer Pro”κΖ¥”Π Ϋ≤β ‘Χ®…ζ≥…

TestBencher Pro¥¥Ϋ®Μυ”Ύ ¬ΈώΒΡ≤β ‘Χ®

SPICE≤β ‘Χ®ΦΛάχΘ®ΡΘΡβΚΆ ΐΉ÷Θ©

2ΓΔ‘ΎVhdlΚΆVerilog

V2V ÷°ΦδΫχ––Ζ≠“κΘΚΉ‘ΦΚΕ· ÷Ζ≠“κΙΛΨΏ

»ΪΖΫΈΜΖΰΈώΒΡVHDLΚΆVerilogΖ≠“κΘΚΈ“Ο«ΈΣΡζΖΰΈώ

3ΓΔΡΘΡβΚΆΒς ‘VHDLΚΆVerilog…ηΦΤ

VeriLogger ExtremeΘΚΗΏ–‘ΡήVerilog 2001Ζ¬’φΤς

BugHunter ProΘΚ ”Ο”ΎΥυ”–HDLΖ¬’φ

ΤςΒΡΆΦ–ΈΒς ‘ΤςGigawave ViewerΘΚVCD / SPICE≤®–Έ≤ιΩ¥ΤςΕ·Χ§

Ο≈ΘΚΆχ±μΖ÷ΈωΤς

4ΓΔ¥¥Ϋ®ΚΆΒΦΚΫVerilogΚΆVHDL¥ζ¬κ

«αΥ…ΘΚΉ¥Χ§ΆΦΚΆΩρΆΦ±ύΦ≠Τς

HDLΑ鬬ΘΚΧΫΥςΚΆ¥¥Ϋ®VHDLΚΆVerilog…ηΦΤ

IO CheckerΘΚ―ι÷ΛFPGAΚΆPCB÷°ΦδΒΡ ΐΑΌΗω“ΐΫ≈

5ΓΔ≤ιΩ¥≤®–Έ≤ΔΫΪΤδΒΦ≥ωΒΫΘΚ

Α≤Ϋί¬Ή≤β ‘…η±ΗΘ§ Χ©ΩΥ≤β ‘…η±ΗΘ§

ΡΘΡβΚΆ ΐΉ÷ΡΘΡβΤς

6ΓΔΜφ÷ΤΚΆΖ÷Έω ±–ρΆΦ

DataSheet ProΘΚΉ®“Β ΐΨί±μ±ύΦ≠Τς

WaveFormer ProΘΚ ±–ρΆΦ±ύΦ≠ΤςΚΆ≤®–ΈΉΣΜΜΤς

Timing Diagrammer ProΘΚ ±–ρΆΦ±ύΦ≠Τς

–¬ΙΠΡήΫι…ή

1ΓΔœνΡΩΦΕΙΠΡή

Project Window÷–ΒΡNew Port MappingsΚΆParm MappingsΈΡΦΰΦ–œ‘ ΨΝΥ≤β ‘ΡΘ–Ά»γΚΈΝ§Ϋ”ΒΫ≤β ‘ΤΫΧ®ΓΘ¥ΥΆβΘ§»Ο”ΟΜßΗϋΗΡ”≥…δΓΘ

Port MappingsΆΦ±ξ―’…Ϊ÷Η Ψ”≥…δ «Ρ§»œ”≥…δΘ®¬Χ…ΪΘ©ΜΙ «Ή‘Ε®“ε”≥…δΘ®≥»…ΪΘ©ΓΘ‘ΎΡ§»œ”≥…δ÷–Θ§‘Ύ≤β ‘ΤΫΧ®÷–¥¥Ϋ®ΒΡ–≈Κ≈”κ±Μ≤βΡΘ–Ά÷–ΕΥΩΎΒΡ»Ζ«–Οϊ≥ΤœύΤΞ≈δΓΘΒ±Ρζœκ“Σ≤β ‘÷ν»γΝΫΗωΦΕΝΣ≤Δ––Φ”Ζ®ΤςΒγ¬Ζ÷°άύΒΡ…ηΦΤΕχ≤Μ Ήœ»¥¥Ϋ®ΑϋΉΑΝΫΗωΦ”Ζ®ΤςΒΡΡΘΩι ±Θ§Ή‘Ε®“ε”≥…δΜαΚή”–”ΟΓΘ

2ΓΔBuHunterΙΠΡή

tep OverΚΆStep IntoΑ¥≈ΞΫΪΤτΕ·ΡΘΡβΤςΘ®»γΙϊ…–Έ¥ΤτΕ·Θ©ΓΘ

GUI‘ –μΡζ‘ΎΡΘΡβΆξ≥…Κσ≤ι―·ΡΘΡβΉ¥Χ§Θ§÷±ΒΫΡζΑ¥œ¬Κλ…Ϊ“Ϋα χΡΘΡβ”Α¥≈ΞΓΘ±Ί–κœ»Α¥“Ϋα χΡΘΡβ”Α¥≈ΞΘ§»ΜΚσ≤≈ΡήΩΣ Φ–¬ΒΡΡΘΡβΓΘ

ΈΣGUIΧμΦ”ΝΥΡΘΡβΒς”ΟΕ―’Μœ‘ ΨΓΘ’βΕ‘”ΎΒς ‘»ΈΈώΚΆΚ· ΐΒΡΒς”ΟΚή”–”ΟΓΘ

3ΓΔ ±–ρΆΦΦΕ±πΙΠΡή

‘ΎœνΡΩ¥ΑΩΎ÷–œ‘ ΨΑϋ±δΝΩ“‘±ψ”ΎΒς ‘ΓΘ

‘Ύ“œνΡΩ”≤ΥΒΞ÷–ΧμΦ”ΝΥ“ΒΦ≥ω ±–ρΆΦ”Θ§“‘ΫΪœνΡΩ÷–Ν–≥ωΒΡΥυ”– ±–ρΆΦΒΦ≥ωΈΣΧΊΕ®Ηώ ΫΓΘ ¥ΥΙΠΡή ”Ο”ΎWaveFormer ProΚΆDataSheet ProΓΘ «κ≤ΈΦϊΒΎ11.3ΫΎ“ΒΦ≥ω“ΜΑψΥΒΟς”ΓΘ

–¬ΒΡΟϋΝν––―Γœν-MΫΪΒΎΕΰΗω ±–ρΆΦΚœ≤ΔΒΫ’ΐ‘ΎΦ”‘ΊΒΡ ±–ρΆΦΘ®“‘«Α¥ΥΙΠΡή÷ΜΡή¥”GUIΖΟΈ Θ§œ÷‘ΎΩ…“‘ΉςΈΣ≈ζ¥Πάμ≤ΌΉς÷¥––Θ©ΓΘ

ά©’ΙVCDΈΡΦΰΒΦ»κΦφ»ί–‘ΓΘ

ΙΠΡήΧΊ…Ϊ

“ΜΓΔTestBencher Pro

1ΓΔVHDLΘ§VerilogΚΆTestBuilderΆΦ–Έ≤β ‘ΤΫΧ®…ζ≥…

TestBencher Pro «“ΜΗωΆΦ–ΈΜ·ΒΡ≤β ‘ΤΫΧ®…ζ≥…ΤςΘ§Ω…“‘¥σ¥σΦθ…Ό¥¥Ϋ®ΚΆΈ§ΜΛ≤β ‘ΤΫΧ®Υυ–ηΒΡ ±ΦδΓΘΕ‘”ΎHDL”ο―‘”ΟΜßά¥ΥΒΘ§ΉνΚΡ ±ΒΡ»ΈΈώ÷°“Μ «Ε‘≤β ‘ΤΫΧ®Ϋχ––±ύ¬κΘ§“‘―ι÷ΛΤδ…ηΦΤΒΡ‘Υ––«ιΩωΓΘJanick Bergeron‘ΎΥϊΒΡΓΕ±ύ–¥≤β ‘ΤΫΧ®ΓΖ“Μ ι÷–ΙάΦΤΘ§”–70ΘΞΒΡ…ηΦΤ ±Φδ”Ο”Ύ―ι÷ΛHDL¥ζ¬κΡΘ–ΆΘ§≤Δ«“≤β ‘ΤΫΧ®’Φ≤ζΤΖΩΣΖΔΙΐ≥Χ÷–…ζ≥…ΒΡ»Ϊ≤ΩHDL¥ζ¬κΒΡ80ΘΞΓΘ

TestBencher Pro Ι≤β ‘Χ®ΩΣΖΔ÷–ΉνΖ±ΥωΒΡΙΛΉςΉ‘Ε·Μ·Θ§¥”Εχ ΙΡζΩ…“‘Ή®ΉΔ”Ύ≤β ‘Χ®ΒΡ…ηΦΤΚΆ≤ΌΉςΓΘ’β «Ά®Ιΐ“‘ΆΦ–ΈΖΫ Ϋ±μ ΨΟΩΗωΉήœΏ ¬ΈώΘ§»ΜΚσΉ‘Ε·ΈΣΟΩΗω ¬Έώ…ζ≥…¥ζ¬κά¥ Βœ÷ΒΡΓΘTestBencherάϊ”ΟΥυ…ζ≥…”ο―‘ΒΡ«Ω¥σΙΠΡήΘ§ΕχΙΛ≥Χ Π≤Μ±Ί ÷Ε·±ύ¬κΟΩΗω ¬ΈώΓΘ‘ΎΫχ–– ÷ΙΛ±ύ¬κ ±Θ§…ηΦΤ»Υ‘±ΫΪ≤ΜΒΟ≤ΜΜ® ±Φδ¥Πάμ…ηΦΤœΗΫΎΘ®ΕΥΩΎ–≈œΔΘ§Φύ ”œΒΆ≥œλ”ΠΒ»Θ©“‘ΦΑ≥ΘΦϊΒΡ±ύ≥Χ¥μΈσΘ®ΨΚ»ϋΧθΦΰΘ§¥Έ“Σ¬ΏΦ≠¥μΈσΚΆ¥ζ¬κ…ηΦΤΈ ΧβΘ©ΓΘ

1ΓΔœΒΆ≥ΦΕΙΠΡή

TestBencherΩ…Ή‘Ε·÷¥––≤β ‘ΤΫΧ®ΩΣΖΔ÷–ΉνΖ±ΥωΒΡΖΫΟφΘ§ ΙΡζΩ…“‘Ή®ΉΔ”Ύ≤β ‘ΤΫΧ®ΒΡ…ηΦΤΚΆ≤ΌΉςΓΘ’β «Ά®Ιΐ“‘ΆΦ–ΈΖΫ Ϋ±μ ΨΟΩΗωΉήœΏ ¬ΈώΘ§»ΜΚσ…ζ≥… ¬Έώ¥ζ¬κά¥Άξ≥…ΒΡΓΘ

VHDLΘ§VerilogΚΆSystemC”ο―‘…ζ≥…ΓΘ

Ά®ΙΐΆΦ–Έ ±–ρΆΦ…ζ≥…ΉήœΏΙΠΡήΡΘ–ΆΓΘ

÷ß≥÷≤ψ¥ΈΡΘ–ΆΓΘ

ΕύΉιΦΰ ΒάΐΜ·÷ß≥÷ΕύΕΥΩΎ…ηΦΤΓΘ

ΡΎ÷ΟΒΡ ±–ρΆΦ±ύΦ≠ΤςΘ§”Ο”Ύ¥¥Ϋ®ΉήœΏ ¬ΈώΓΘ

ΐΨί‘¥ΚΆΡΩ±ξΜαΉ‘Ε·…ζ≥…Υυ”–ΈΡΦΰI / O¥ζ¬κΚΆάύΕ®“εΓΘ

–ρΝ– Ε±π―ι÷Λ ±–ρ–ρΝ–ΓΘ

ΝςΥ°œΏ ¬ΈώΩ…”Ο”Ύ Βœ÷ΝςΥ°œΏΉήœΏ÷ςΩΊΤςΓΘ

Μυ”Ύ÷ήΤΎΚΆ ¬ΦΰΒΡ≤β ‘ΤΫΧ®ΓΘ

2ΓΔΖ¥”Π ΫΖ¬’φΦλ≤ι

Ι”Ο“ΈόΙΠ≤β ‘ΤΫΧ®…ζ≥…”Θ§”ΟΜßΩ…“‘―Γ‘ώ‘ΎMUT δ≥ωΕΥΩΎ…œΜφ÷Τ“‘ΛΤΎ”≤®–ΈΘ§≤Δ‘Ύ≤®–Έ÷–ΧμΦ”“―υ±Ψ”“‘≤β ‘ΧΊΕ®«ιΩωΓΘ‘ΎΖ¬’φΙΐ≥Χ÷–Θ§―υ±Ψ…ζ≥…ΒΡ¥ζ¬κΫΪΙέ≤λ±Μ≤βΡΘ–ΆΒΡ δ≥ωΘ§≤ΔΫΪΤδ”κΜφ÷ΤΉ¥Χ§Ϋχ––±»ΫœΓΘ―υ±ΨΩ…“‘÷¥––Ης÷÷ΙΠΡήΘ§άΐ»γ‘ίΆΘΡΘΡβ“‘Βς ‘Έ ΧβΘ§±®Ηφ¥μΈσΚΆΨ·ΗφΘ§”ΟΜßΕ®“εΒΡ≤ΌΉς“‘ΦΑ¥ΞΖΔΤδΥϊ―υ±ΨΓΘ

3ΓΔΖ¥”ΠΜΖ”–ΧθΦΰΒΊ ©Φ”¥ΧΦΛ

Ζ¥”Π Ϋ≤β ‘ΜυΉΦ…ζ≥…ΜΙΑϋά®Ω…”Ο”ΎΒ»¥ΐ±Μ≤βΡΘ–ΆΒΡΜνΕ·ΚΆ/Μρ‘ΎΆΦΒΡ“Μ≤ΩΖ÷…œ―≠ΜΖΒΡ±ξΦ«ΓΘ±ξΦ«ΜΙΩ…“‘”Ο”Ύ¥”ΆΦ÷–Βς”Ο”ΟΜß±ύ–¥ΒΡHDLΚ· ΐΚΆ»ΈΈώΓΘ

4ΓΔΜυ”Ύ ±÷”ΚΆ ±ΦδΒΡ≤β ‘ΤΫΧ®…ζ≥…

Ζ¥”Π–‘≤β ‘Χ®…ζ≥…ΜΙ‘ –μ¥¥Ϋ®“Μυ”Ύ ±÷”ΒΡ”≤β ‘Χ®“‘ΦΑΜυ”ΎΦΛάχΒΡ…ζ≥…ΡΘ–ΆΒ±«Α÷ß≥÷ΒΡ“Μυ”Ύ ±ΦδΒΡ”≤β ‘Χ®ΓΘΜυ”Ύ ±÷”ΒΡ≤β ‘Χ®―”≥Ό ±÷”÷ήΤΎΕχ≤Μ « ±ΦδΘ§¥”Εχ‘ –μ”ΟΜßΗϋΗΡΤδ ±÷”ΤΒ¬ ΕχΈό–ηΗϋΗΡΤδ ±–ρΆΦΓΘ Ι”ΟΗΏΥΌ“Μυ”Ύ÷ήΤΎ”ΒΡΡΘΡβΤςΫχ––≤β ‘ ±Θ§ΜΙ–η“ΣΜυ”Ύ ±÷”ΒΡ≤β ‘Χ®ΓΘ

ΕΰΓΔWaveFormer Pro

WaveFormer Pro «“Μ÷÷ΗοΟϋ–‘ΒΡ–¬–ΆΩλΥΌ‘≠–ΆΜ·EDAΙΛΨΏΘ§Ω…Αο÷ζΡζΗϋΩλΒΊ…ηΦΤ≤ΔΦθ…Ό¥μΈσΓΘWaveFormer Pro ΙΡζΡήΙΜΉ‘Ε·»ΖΕ®ΙΊΦϋ¬ΖΨΕΘ§―ι÷Λ ±–ρ‘ΘΕ»Θ§’κΕ‘÷Ί–¬ ’Ν≤ΒΡ…»≥ω–ß”ΠΫχ––Βς’ϊ“‘ΦΑ÷¥––“ΦΌ…ηΖ÷Έω”“‘»ΖΕ®ΉνΦ― ±÷”ΥΌΕ»ΓΘWaveFormer ProΜΙ‘ –μΡζ÷ΗΕ®ΚΆΖ÷ΈωœΒΆ≥ ±–ρ≤Δ÷¥––≤ΦΕϊΦΕΖ¬’φΘ§ΕχΈό–η‘≠άμΆΦΜρΖ¬’φΡΘ–ΆΓΘ ±–ρΆΦΆξ≥…ΚσΘ§ΡζΩ…“‘ΈΣΉ‘ΦΚœ≤ΜΕΒΡVerilogΘ§VHDLΘ§SPICEΜρΟ≈ΦΕΖ¬’φΤς…ζ≥… ΐΉ÷ΦΛάχΓΘWaveFormer ProΜΙΨΏ”–ΒΦ»κΚΆΉΔ ΆΖ¬’φΚΆ¬ΏΦ≠Ζ÷Έω“« ΐΨίΒΡΙΠΡήΘ§”Ο”ΎΖΔ≤Φ÷ ΝΩ…ηΦΤΈΡΒΒΓΘ

1ΓΔΡΘΡβ–≈Κ≈

WaveFormer ProΘ§DataSheetProΘ§VeriLoggerΚΆTestBencher ProΨΏ”–ΡΎ÷ΟΒΡΫΜΜΞ ΫHDLΡΘΡβΤςΘ§Ω…¥σ¥σΦθ…ΌΜφ÷ΤΚΆΗϋ–¬ ±–ρΆΦΥυ–ηΒΡ ±ΦδΓΘ Ι”Ο“‘VHDLΘ§VerilogΜρSynaptiCAD”οΖ®±ύ–¥ΒΡ≤ΦΕϊ¬ΏΦ≠ΚΆΉΔ≤α¬ΏΦ≠ΖΫ≥Χ ΫΘ§ΡζΩ…“‘ΗυΨίΆΦ÷–ΒΡΤδΥϊ–≈Κ≈ά¥Οη ω–≈Κ≈ΓΘΡζΫΪ≤Μ‘Ό–η“Σ ÷ΙΛΦΤΥψΉιΚœΒγ¬ΖΒΡ δ≥ωΜρΦΤΥψΆ§≤ΫΒγ¬ΖΒΡΙΊΦϋ¬ΖΨΕΓΘSynaptiCADΒΡΫΜΜΞ ΫΡΘΡβΤςΫΪ Ι”Ο‘ΎLogic WizardΕ‘ΜΑΩρ÷– δ»κΒΡ–≈œΔ…ζ≥…HDL¥ζ¬κΘ§»ΜΚσΡΘΡβΫαΙϊΓΘ”…”ΎΡΘΡβΤς «ΫΜΜΞ ΫΒΡΘ§

ΨΓΙήVeriLoggerΚΆTestBencher≤ζΤΖΨΏ”–ΡΎ÷ΟΒΡVerilogΡΘΡβΤςΘ§ΒΪΗΟΙΠΡή»‘ΑϋΚ§‘ΎΤδ÷–Θ§“ρΈΣΥϋ Ι…ζ≥…≤β ‘Χ®ΦήΚΆ ±–ρΆΦΒΡΥΌΕ»»γ¥Υ÷°ΩλΘ§“‘÷Ν”ΎΈ“Ο«ΈόΖ®»Χ ήΓΘ‘ΎWaveFormer÷–Θ§Υϋ « ±–ρΖ÷ΈωΚΆ…ηΦΤΙΠΡήΒΡΜυ¥ΓΓΘΫΜΜΞ ΫΡΘΡβΤς÷ß≥÷ΕύΈΜΖΫ≥Χ ΫΚΆ’φ ΒΒΡΉν–Γ-Ήν¥σ ±–ρΓΘ

2ΓΔ≤®–ΈΉΣΜΜΙΠΡή

WaveFormer ProΚΆDataSheet Pro÷ß≥÷≥§Ιΐ55÷÷≤ΜΆ§ΒΡΗώ ΫΘ§”Ο”ΎΒΦ»κΚΆΒΦ≥ω≤®–Έ ΐΨίΓΘ¥”ΡΘΡβΤςΘ§¬ΏΦ≠Ζ÷Έω“«ΚΆ ±–ρΖ÷Έω≥Χ–ρΒΦ»κ≤®–Έ ΐΨίΓΘΫΪ≤®–ΈΒΦ≥ωΒΫVHDLΘ§VerilogΘ§SPICEΘ§¬κ–ΆΖΔ…ζΤςΘ§ATEΚΆFPGAΙΛΨΏΓΘ’β–© ±–ρΆΦ±ύΦ≠ΤςΜΙΗΫ¥χΝΥΜυ”ΎPERLΒΡΫ≈±Ψ”ο―‘Θ§ ΙΙΛ≥Χ ΠΩ…“‘¥¥Ϋ®Ή‘ΦΚΒΡΒΦ»κΚΆΒΦ≥ωΫ≈±ΨΘ§“‘÷ß≥÷Ε®÷Τ≤β ‘…η±ΗΚΆΡΎ≤ΩΩΣΖΔΒΡ»μΦΰ Ι”ΟΒΡ≤®–ΈΗώ ΫΓΘ

3ΓΔΜυ±Ψ ±–ρΆΦ±ύΦ≠ΙΠΡή

Μφ÷ΤΚΆ±ύΦ≠ ±–ρΆΦ

±–ρΖ÷ΈωΙΠΡή

ΡΘΡβ≤®–Έ÷ß≥÷

≤®–ΈΚΆ±ξ«©ΖΫ≥Χ

ΈΡΒΒΙΠΡή

≈ζ¥ΠάμΡΘ Ϋ≤ΌΉς

4ΓΔ≤®–Έ±»Ϋœ―Γœν

≤®–Έ±»Ϋœ «“ΜœνΩ…―ΓΙΠΡήΘ§Υυ”–SynaptiCAD ±–ρΆΦ±ύΦ≠ΤςΚΆΆΦ–Έ≤ζΤΖΨυΩ……ΐΦΕΈΣΑϋΚ§¥ΥΙΠΡήΓΘ≤®–Έ±»ΫœΙΠΡή“‘ΆΦ–ΈΖΫ Ϋœ‘ ΨΝΫΗω ±–ρΆΦΜρΒΞΗω–≈Κ≈ΒΡ≤®–Έ÷°ΦδΒΡ≤ν“λΓΘ±»ΫœΝΫΗω≤ΜΆ§ΒΡΖ¬’φ‘Υ––“‘ΦΑΫΪ¬ΏΦ≠Ζ÷Έω“« ΐΨί”κΖ¬’φ‘Υ––Ϋχ––±»Ϋœ ±Θ§¥ΥΙΠΡήΧΊ±π”–”ΟΓΘ≤ν“λœ‘ ΨΈΣ±»Ϋœ–≈Κ≈…œΒΡΚλ…Ϊ«χ”ρΓΘ”–»ί≤ν«χ”ρΚΆΕ® ±±»ΫœΒΡ…η÷ΟΘ§“‘Αο÷ζ¬Υ≥ΐ≤Μ÷Ί“ΣΒΡ≤ν“λΓΘ

»ΐΓΔVerilogger Pro

VerilogΡΘΡβΤςΩ…ΧαΙ©ΉνΦ―Βς ‘ΓΘ

ΉΦ»Ζ–‘ΚΆ ±Φδ÷ΝΙΊ÷Ί“ΣΘ§”»Τδ «‘ΎΩΣΖΔΖ¬’φΚΆΒς ‘ΖΫΟφΓΘΈ“Ο«ΒΡVerilogΡΘΡβΤςΚΆ±ύ“κΤςΫΪΗΡ±δΡζΡΘΡβΘ§Βς ‘ΚΆΙήάμΩΣΖΔΙΐ≥ΧΒΡΖΫ ΫΓΘ

VeriLogger Extreme «ΗΏ–‘ΡήΒΡVerilog 2001±ύ“κ¥ζ¬κΡΘΡβΤςΘ§ΨΏ”–Ή‘Ε·≤β ‘ΤΫΧ®…ζ≥…ΙΠΡήΘ§Ω…œ‘Ή≈Φθ…ΌΖ¬’φΒς ‘ ±ΦδΓΘVeriLogger Extremeάϊ”ΟSDF ±–ρ–≈œΔΧαΙ©RTLΚΆΟ≈ΦΕΖ¬’φΒΡΩλΥΌΖ¬’φΓΘVeriLogger Extreme÷ß≥÷Υυ”–÷ς“ΣASICΚΆFPGAΙ©”Π…ΧΒΡ…ηΦΤΩβΚΆ…ηΦΤΝς≥ΧΘ§Αϋά®Actel / MicroSemiΘ§AlteraΘ§AtmelΘ§LSI LogicΘ§QuickLogicΚΆXilinxΓΘ

Α≤ΉΑΤΤΫβΫΧ≥Χ

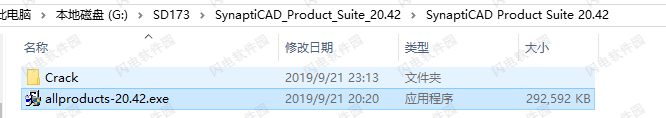

1ΓΔ‘Ύ±Ψ’Ψœ¬‘Ί≤ΔΫβ―ΙΘ§»γΆΦΥυ ΨΘ§ΒΟΒΫallproducts-20.42.exeΑ≤ΉΑ≥Χ–ρΚΆcrackΤΤΫβΈΡΦΰΦ–

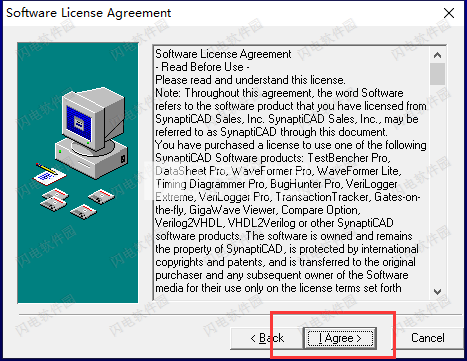

2ΓΔΥΪΜςallproducts-20.42.exe‘Υ––Θ§–μΩ…–≠“ιΘ§ΒψΜςi a'geee

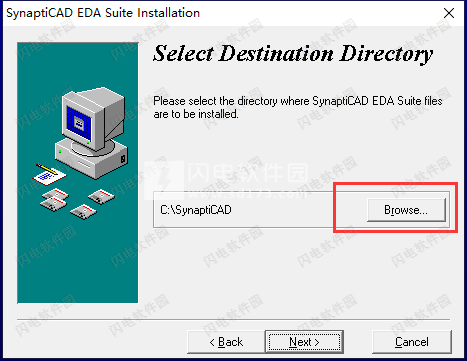

3ΓΔ―Γ‘ώ»μΦΰΑ≤ΉΑ¬ΖΨΕΘ§ΒψΜςnext

4ΓΔΑ≤ΉΑ ±Φδ±»ΫœΨΟΘ§ΡΆ–ΡΒ»¥ΐΘ§Α≤ΉΑΆξ≥…Θ§ΒψΜςfinishΆΥ≥ωœρΒΦ

5ΓΔΫΪcrack÷–ΒΡsyncad.licΟή‘ΩΈΡΦΰΖ≈»κΑ≤ΉΑΡΩ¬Φ÷–Φ¥Ω…

Ι”ΟΑο÷ζ

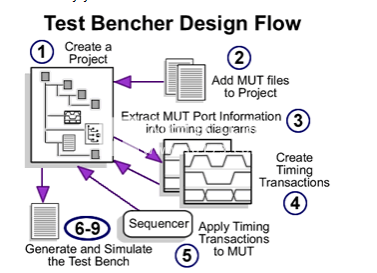

TestBencher Pro…ηΦΤΝς≥Χ±Ψ’¬ΫΪΫι…ή Ι”ΟTestBencher Pro…ζ≥… ¬ΈώΦΕ±πΡΘ–ΆΘ®TLMΘ©ΒΡΜυ±Ψ…ηΦΤΝς≥ΧΓΘ Ήœ»Θ§ΡζΫΪ¥¥Ϋ®“ΜΗω–¬ΒΡœνΡΩΈΡΦΰΘ§≤ΔΧμΦ””–ΙΊ±Μ≤βΡΘ–ΆΘ®MUTΘ©ΈΡΦΰΒΡ–≈œΔΓΘ Ϋ”œ¬ά¥Θ§ΡζΫΪ¥¥Ϋ® ±–ρΆΦΘ§“‘…ζ≥…Ω…÷ΊΗ¥ Ι”ΟΒΡ ±–ρ ¬ΈώΓΘ »ΜΚσΘ§ΡζΫΪ±ύΦ≠ΕΞΦΕΡΘ–ΆΘ§≤ΔΕ®“εΫΪ ¬Έώ”Π”Ο”ΎMUTΒΡΥ≥–ρΓΘ ΉνΚσΘ§ΡζΫΪΡΘΡβ≤β ‘Χ®ΓΘ

“ΜΓΔ¥¥Ϋ®“ΜΗω–¬œνΡΩ

œνΡΩΑϋΚ§…ζ≥…TestBencherPro ¬ΈώΦΕ±πΡΘ–ΆΘ®TLMΘ©Υυ–ηΒΡΥυ”––≈œΔΘ§Αϋά® ¬ΈώΆΦ±μΘ§ΕΞΦΕΈΡΦΰΚΆ¥ζ¬κ…ζ≥……η÷ΟΓΘΒΎ9’¬ΘΚTestBencherΗΏΦΕœνΡΩΙΠΡήΫι…ήΝΥœνΡΩΘ§Ή”œνΡΩΚΆ¥¥Ϋ®œνΡΩ ΒάΐΓΘ“‘œ¬ «¥¥Ϋ®Μυ±ΨΒΞΦΕœνΡΩΒΡ≤Ϋ÷ηΓΘ

¥¥Ϋ®“ΜΗωœνΡΩΘΚ

·―Γ‘ώœνΡΩ>–¬Ϋ®œνΡΩ≤ΥΒΞ―ΓœνΓΘ’βΫΪ¥ρΩΣ“–¬Ϋ®œνΡΩœρΒΦ”Ε‘ΜΑΩρΓΘ

·“œνΡΩΟϊ≥Τ”Φ» «œνΡΩΒΡΟϊ≥ΤΘ§“≤ «œνΡΩΒΡ¥φ¥ΔΡΩ¬ΦΓΘ

·Φλ≤ιΜυ”Ύ ¬ΈώΒΡ≤β ‘ΤΫΧ®ΒΡ…ζ≥…Θ§“‘ ΙTestBencher…ζ≥… ¬ΈώΦΕ±πΒΡΡΘ–ΆΘ§Εχ≤Μ «ΒΞΗωΆΦ≤β ‘ΤΫΧ®ΓΘ

·“”ο―‘”œ¬ά≠Ν–±μΕ®“εΝΥ≤β ‘ΤΫΧ®ΡΘ–ΆΒΡ…ζ≥…”ο―‘ΓΘΡ≥–©ΙΠΡήΘ®άΐ»γ”––ß–≈Κ≈άύ–ΆΘ©»ΓΨω”Ύ…ζ≥…ΒΡ”ο―‘Θ§“ρ¥Υ¥Υ―ΓœνΜα”ΑœλTestBencherΒΡ≤ΌΉςΓΘ

·Α¥“œ¬“Μ≤Ϋ”Α¥≈Ξ“Τ÷ΝΕ‘ΜΑΩρΒΡœ¬“Μ“≥ΓΘ

·»γΙϊΡζΒΡœνΡΩ“―ΦΤ ±Θ§«κΦϋ»κ ±÷”–≈Κ≈ΒΡΟϊ≥ΤΘ§“‘±ψΗΟœνΡΩΫΪΈΣ ±÷”…ζ≥…“ΜΗωΧΊ βΒΡ ¬Έώ¥Πάμ≥Χ–ρΓΘ

·Α¥“Ρ§»œΆΦ…η÷Ο”Α¥≈Ξ±ύΦ≠–¬ΆΦΒΡΡ§»œΆΦ…η÷ΟΓΘ

·Ρ§»œ«ιΩωœ¬Θ§…ηΦΤΒΡ“ ±÷”±Ώ‘ΒΚσΡ§»œ―”≥Ό”…η÷ΟΙΧΕ®ΈΣ0ΒΡ―”≥Ό ±ΦδΓΘ”–ΙΊ»γΚΈ Ι”Ο¥Υ…η÷ΟΒΡ–≈œΔΘ§«κ≤ΈΦϊΒΎ9.8ΫΎΘΚ“ΆΦ…η÷Ο”Ε‘ΜΑΩρΘ®Ϋω ”Ο”ΎTestBencherΘ©ΓΘ

·Α¥“Άξ≥…”Α¥≈ΞΙΊ±’“–¬Ϋ®œνΡΩœρΒΦ”≤Δ¥¥Ϋ®–¬œνΡΩΓΘ

«κΉΔ“βΘ§TestBencherΜαΉ‘Ε·¥ρΩΣ“œνΡΩ”¥ΑΩΎΘ§≤Δ Ι”ΟΕΞΦΕΡΘΑεΈΡΦΰΚΆΡΘΑεΆΦΧν≥δΥϋΓΘΡΘΑεΆΦ «ΡζΧμΦ”ΒΫœνΡΩ÷–ΒΡ»ΈΚΈ–¬ ¬ΈώΒΡΤπΒψΓΘ“œνΡΩ”¥ΑΩΎΫΪ «Ρζδ·άά ¬ΈώΦΕ±πΡΘ–ΆΒΡ≤ΜΆ§≤ΩΖ÷ΒΡ÷ς“ΣΉ ‘¥ΓΘ

“œνΡΩ”¥ΑΩΎΒΡΜυ±ΨΩΊΦΰΘΚ

·”“ΦϋΒΞΜς“œνΡΩ” ς÷–ΒΡ»ΈΚΈΫΎΒψΘ§“‘¥ρΩΣ“ΜΗω…œœ¬ΈΡœύΙΊΒΡΒ·≥ω≤ΥΒΞΘ§Τδ÷–ΑϋΚ§Ω…“‘Ε‘ΗΟΧΊΕ®ΫΎΒψάύ–Ά÷¥––ΒΡΥυ”–≤ΌΉςΓΘ

·‘Ύ»ΈΚΈΫΎΒψ…œΒΞΜς σ±ξΉσΦϋ“‘Ε‘ΗΟΫΎΒψ÷¥––Ρ§»œ≤ΌΉςΘ®Ά®≥Θ‘Ύ Β±ΒΡ±ύΦ≠Τς÷–¥ρΩΣΗΟΈΡΦΰΜρΕ‘œσΘ©ΓΘ

·“Σ’ΙΩΣΜρ“ΰ≤Ί ςΒΡΖ÷÷ßΘ§«κΒΞΜςexpandNodeΜρcollapseNodeΓΘ

·ΆœΖ≈Ν–±ξΧβ“‘Βς’ϊΝ–¥σ–ΓΓΘ

“œνΡΩ”¥ΑΩΎΒΡ“Μυ±ΨΈΡΦΰΦ–”ΘΚ

ΟΩΗωœνΡΩ÷–ΕΦΜα¥¥Ϋ®ΦΗΗωΈΡΦΰΦ–Θ§’β–©ΈΡΦΰΦ–”Ο”ΎΉι÷·≤β ‘ΤΫΧ®≤ΜΆ§ΦΕ±πΒΡΈΡΦΰΚΆΕ‘œσΓΘ’β–©ΈΡΦΰΦ–÷–ΒΡΟΩ“ΜΗωΫΪ‘Ύ ÷≤αΒΡ≤ΜΆ§ΒΊΖΫΫχ––Χ÷¬έΓΘΉςΈΣΗ≈ ωΘΚ

·“ΡΘΡβΡΘ–Ά”ΈΡΦΰΦ–ΑϋΚ§Άξ’ϊΒΡ±ύ“κ…ηΦΤΘ§“ΦΛάχΚΆΫαΙϊ”ΆΦ“‘ΦΑά¥Ή‘ΡΘΡβΤςΒΡ»’÷ΨΈΡΦΰΓΘ”–ΙΊΗϋΕύ–≈œΔΘ§«κ≤ΈΦϊΒΎ8’¬ΘΚ…ζ≥…ΚΆΖ¬’φΓΘΗΟ«χ”ρ”Ο”ΎΖ÷ΈωΚΆΒς ‘“―±ύ“κΒΡΖ¬’φΓΘ

·±Μ≤βΡΘ–ΆΑϋΚ§¥χ”–ΕΥΩΎΒΡΡΘ–ΆΘ§’β–©ΕΥΩΎΫΪΝ§Ϋ”ΒΫ≤β ‘Χ®ΓΘΡ§»œ«ιΩωœ¬Θ§Β±Α¥œ¬“Χα»ΓMUTΕΥΩΎ”Α¥≈Ξ ±Θ§Έ¥ ΒάΐΜ·‘ΎΝμ“ΜΗωΡΘ–Ά÷–ΒΡΒΎ“ΜΗωΡΘ–Ά±Μ―Γ‘ώΈΣ≤β ‘÷–ΒΡΡΘ–ΆΓΘΒΎ“Μ¥ΈΙΙΫ®ΚσΘ§ΡζΩ…“‘―Γ‘ώ”“ΦϋΒΞΜςΤδΥϊΡΘΩιΘ§»ΜΚσ―Γ‘ώ“…η÷ΟΈΣ≤β ‘÷–ΒΡΡΘ–Ά”“‘ΩΊ÷Τ‘Ύ≤β ‘ΤΫΧ®÷– ΒάΐΜ·ΒΡΡΘ–ΆΓΘ”–ΙΊΗϋΕύ–≈œΔΘ§«κ≤ΈΦϊ≤Ϋ÷η3ΘΚΫΪΕΥΩΎΧα»ΓΒΫΡΘΑεΆΦ÷–ΓΘ

§ΕΥΩΎ”≥…δΚΆ≤Έ ΐ”≥…δœ‘ ΨΝΥ»γΚΈΝ§Ϋ”ΡΘ–ΆΓΘΡ§»œ«ιΩωœ¬Θ§ΨΏ”–œύΆ§Οϊ≥ΤΒΡ–≈Κ≈Μα”≥…δ‘Ύ“ΜΤπΓΘΡζΩ…“‘Ά®Ιΐ“‘œ¬ΖΫ ΫΉ‘Ε®“ε”≥…δ

· ¬ΈώΦΕ±πΡΘ–Ά «≤β ‘ΤΫΧ®ΒΡΕΞΦΕΡΘΑεΈΡΦΰΓΘΗΟΈΡΦΰΦ–ΑϋΚ§Υυ”–œνΡΩΦΕ±πΒΡάύΘ§±δΝΩΘ§άύΖΫΖ®ΚΆΉ”œνΡΩΒΡ ΒάΐΓΘ”–ΙΊΗϋΕύ–≈œΔΘ§«κ≤ΈΦϊΒΎ7’¬ΘΚ ¬ΈώΦΕΡΘ–Ά ¬ΈώΕ®–ρΤςΓΘ

·“TransactionDiagrams”ΈΡΦΰΦ–ΑϋΚ§ΡΘΑε ±–ρΆΦΘ§“―ΧμΦ”ΒΫœνΡΩ÷–ΒΡ ±–ρΆΦ“‘ΦΑœύΙΊΒΡ…ζ≥…ΒΡ‘¥¥ζ¬κΈΡΦΰΘ®‘Ύ ±–ρΆΦœ¬ΖΫΒΡΦΕ±πΘ©ΓΘ÷ςΆΦ¥χ”–≤®–ΈΆΦ±ξΘ§Εχ¥” τΆΦ¥χ”–ΜΊΥΆΆΦ±ξΓΘ”–ΙΊΗϋΕύ–≈œΔΘ§«κ≤ΈΦϊΒΎ2’¬ΘΚ ±–ρΫΜ“ΉΤςΜυ¥ΓΓΘ

·TestVectorFilesΈΡΦΰΦ–ΑϋΚ§ δ»κΚΆ δ≥ω≤β ‘ ΗΝΩΈΡΦΰΓΘΒΎ8’¬ΘΚάύΚΆ±δΝΩΘ§“‘Μώ»ΓΗϋΕύ–≈œΔΓΘ

·“œνΡΩΩβ”ΈΡΦΰΦ–ΑϋΚ§Ω…‘ΎΒ±«ΑœνΡΩ÷– ΒάΐΜ·ΒΡΥυ”–Ή”œνΡΩΓΘΒΎ9.1ΫΎΘΚΉ”œνΡΩΧ÷¬έΝΥΗΟΈΡΦΰΦ–ΓΘ

·“”ΟΜß‘¥ΈΡΦΰ”ΈΡΦΰΦ–ΑϋΚ§“Σ‘Ύ≤β ‘ΤΫΧ®÷– Ι”ΟΒΡ‘¥ΈΡΦΰΓΘ¥χ”–¬Χ…ΪΗ¥―Γ±ξΦ«ΆΦ±ξΒΡΈΡΦΰ“―±Μ±ύ“κΒΫ≤β ‘Χ®÷–ΓΘ¥χ”–Κλ…ΪXΆΦ±ξΒΡΈΡΦΰ…–Έ¥±Μ±ύ“κ≤Ϋ÷η3ΘΚΫΪMUTΕΥΩΎΧα»ΓΒΫΡΘΑεΆΦ÷–ΨΏ”–ΗϋΕύ–≈œΔΓΘ

ΕΰΓΔΫΪMUTΧμΦ”ΒΫœνΡΩ

…ηΦΤΒΡ±Μ≤βΡΘ–ΆΘ®MUTΘ©ΈΡΦΰ”ΠΧμΦ”ΒΫœνΡΩ÷–ΓΘTestBencherΫΪ Ι”Ο’β–©ΈΡΦΰΫΪMUT ΒάΐΜ·ΒΫΡζΒΡ≤β ‘Χ®÷–Θ§≤ΔΧα»Γ–≈Κ≈ΚΆΕΥΩΎ–≈œΔΘ§“‘”Ο”ΎΦΛΖΔMUTΒΡ ¬ΈώΆΦ÷–ΓΘ

ΫΪMUT‘¥ΈΡΦΰΗ¥÷ΤΜρΧμΦ”ΒΫœνΡΩ÷–ΘΚ

·”“ΦϋΒΞΜς“”ΟΜß‘¥ΈΡΦΰ”ΈΡΦΰΦ–Θ§»ΜΚσΫΪ…ηΦΤΈΡΦΰΧμΦ”ΜρΗ¥÷ΤΒΫœνΡΩ÷–ΓΘ

·“Η¥÷Τ”≤ΥΒΞΫΪ‘¥ΈΡΦΰΗ¥÷ΤΒΫœνΡΩΈΡΦΰΦ–Θ§≤ΔΫΪΗ±±ΨΧμΦ”ΒΫœνΡΩΝ–±μΓΘΧμΦ”ΙΠΡήΧμΦ”ΈΡΦΰΦΑΤδ¬ΖΨΕΕχ≤ΜΫχ––Η¥÷ΤΓΘ“≤Ω…“‘Ά®Ιΐ¥”÷ςάΗ÷–―Γ‘ώ“œνΡΩ”>“ΧμΦ””ΟΜß‘¥ΈΡΦΰ”≤ΥΒΞά¥ΧμΦ”ΈΡΦΰΓΘ

·»γΙϊΡζΒΡMUT–η“Σ¥”±ύ“κΒΫΤδΥϊΩβ÷–ΒΡΑϋ÷–Ε®“εΘ§«κΑ¥’’ΒΎ8.5ΫΎΘΚΫΪΑϋΈΡΦΰΫβΈωΈΣΩβ÷–ΒΡ≤Ϋ÷ηΫχ––≤ΌΉςΘ§“‘»Ζ±Θ’ΐ»ΖΫβΈωΝΥ’β–©ΑϋΓΘ»γΙϊΡζΒΡMUTΫβΈω»Ζ Β–η“ΣΫΪΈΡΦΰ±ύ“κΒΫΕύΗωΩβ÷–Θ§‘ρΩ…Ρή–η“Σ‘ΎΒΎ“Μ¥ΈΫβΈωΚσ÷±Ϋ”…η÷ΟΥυ–ηΒΡ≤β ‘ΡΘ–ΆΘ§»ΜΚσ‘Ό¥ΈΫβΈωΘ®«κ≤Έ‘Ρ≤Ϋ÷η3ΘΚΫΪΕΥΩΎΧα»ΓΒΫΡΘΑε÷–Θ©ΓΘ

Θ®Ω…―ΓΘ© ΒάΐΜ·œνΡΩ÷–ΒΡΕύΗωMUT

»γΙϊΡζΒΡœνΡΩΫωΙ“Ϋ”“ΜΗω‘¥ΡΘ–Ά÷–ΒΡΕΞΦΕΡΘ–ΆΘ§Φ¥±Μ≤βΡΘ–ΆΘ§‘ρΩ…“‘ΧχΙΐ¥ΥΙΐ≥Χ≤ΔΦΧ–χ÷¥––≤Ϋ÷η3ΓΘΒΪ «Θ§¥Υ≤ζΤΖ÷ß≥÷ΕύΗωMUTΚΆΆ§“ΜMUTΒΡΕύΗω ΒάΐΜ·ΓΘΓΘ Ήœ»ΙΙΫ®œνΡΩΘ§»ΜΚσ―Γ‘ώΡζΒΡMUT≤ΔΗυΨί–η“Σ±ύΦ≠–¬MUTΒΡΕΥΩΎ”≥…δΓΘ’β”ΠΗΟ‘Ύ¥¥Ϋ® ¬Έώ÷°«ΑΆξ≥…Θ§“‘±ψ‘Ύ ¬ΈώΙΙΫ®≤Ϋ÷η÷–Ω…“‘ Ι”ΟΥυ”––≈Κ≈ΓΘ

·Α¥“ΙΙΫ®”Α¥≈ΞΖ÷Έω‘¥ΈΡΦΰΘ§≤Δ Ι”ΟΡΘΩι–≈œΔΧν≥δœνΡΩ¥ΑΩΎ ςΓΘ

·…ν»κΒΫ“”ΟΜß‘¥ΈΡΦΰ”ΫΎΒψΘ§»ΜΚσ‘ΎMUT…œΒΞΜς σ±ξ”“Φϋ“‘¥ρΩΣ…œœ¬ΈΡ≤ΥΒΞΓΘ

·―Γ‘ώ“…η÷ΟΈΣ≤β ‘÷–ΒΡΡΘ–Ά”ΓΘ

·«κΉΔ“βΘ§ΗΟΡΘΩι“―ΧμΦ”ΒΫ“¥ΐ≤βΡΘ–Ά” ςΫΎΒψ÷–ΓΘ¬Χ…Ϊ±μ ΨΕΥΩΎ”≥…δ’ΐ‘Ύ Ι”Ο”κMUTΒΡΕΥΩΎΟϊ≥ΤΤΞ≈δΒΡΡ§»œ÷ΒΓΘ

·¥””“ΦϋΒΞΜς…œœ¬ΈΡ≤ΥΒΞΘ®»γ…œΥυ ΨΘ©÷–―Γ‘ώ“≤β ‘÷–ΒΡΩΥ¬ΓΡΘ–Ά”Θ§“‘¥¥Ϋ®MUTΒΡΝμ“ΜΗω ΒάΐΓΘ

·≥Χ–ρΆ®ΙΐΤΞ≈δœύΆ§ΒΡΟϊ≥Τ–≈Κ≈ά¥≤¬≤βΕΥΩΎ”≥…δΓΘΒΪ «Θ§¥””“ΦϋΒΞΜς…œœ¬ΈΡ≤ΥΒΞΘ®»γ…œΥυ ΨΘ©÷–―Γ‘ώ“±ύΦ≠±Μ≤βΡΘ–Ά”Θ§ΫΪ¥ρΩΣ“ΜΗωΕ‘ΜΑΩρΘ§ΗΟΕ‘ΜΑΩρ‘ –μΗϋΗΡΡΘ–Ά ΒάΐΟϊ≥Τ“‘ΦΑΕΥΩΎΚΆ≤Έ ΐ”≥…δΓΘ

·ΥΪΜςΕΥΩΎΟϊ≥ΤΫΪ¥ρΩΣ“ΜΗωœ¬ά≠Ν–±μΘ§ΡζΩ…“‘‘ΎΤδ÷–―Γ‘ώΤδΥϊΕΥΩΎΜρΦϋ»κΤδΥϊΟϊ≥ΤΓΘ

·‘Ύ±ύΦ≠Άξ Βάΐ”≥…δΚσΘ§ ς÷–ΒΡΆΦ±ξΫΪ±δΈΣΚλ…ΪΘ§±μ Ψ»γΙϊœνΡΩ÷–ΖΔ…ζΤδΥϊΗϋΗΡΘ§≥Χ–ρΫΪ≤ΜΜαΗ≤Η«ΕΥΩΎΓΘ

·»γΙϊ“Σ―–ΨΩΡΘ–Ά Βάΐ≤ΔΕ®“ε¥¥Ϋ®ΒΡ»ΈΚΈ–¬–≈Κ≈Θ§«κΑ¥MakeTBΑ¥≈ΞΘ§»ΜΚσΥΪΜς“Transaction-LevelModel”ΫΎΒψ“‘¥ρΩΣ¥χ”–…ζ≥…ΒΡ≤β ‘ΜυΉΦ¥ζ¬κΒΡ±ύΦ≠ΤςΓΘ

·»Ζ±Θ‘Ύ¥ζ¬κ…ζ≥…ΡΘΩι÷°ΆβΕ®“ε–¬–≈Κ≈ΓΘ≤ΔΫΪΥϋΟ«ΧμΦ”ΒΫ$InstantiateMUT¥ζ¬κ…ζ≥…Ωι÷°«ΑΒΡΡ≥ΗωΈΜ÷ΟΓΘ

VHDLΚΆVerilogΜλΚœ…ηΦΤΘΚ

»γΙϊΡζ Ι”ΟΒΡ «Εύ”ο―‘…ηΦΤΘ§Μρ’ΏΡζΗϋœΑΙΏ Ι”ΟΧΊΕ®ΒΡHDL”ο―‘Θ§‘ρ…ζ≥…ΒΡ≤β ‘ΤΫΧ®ΚΆ…ηΦΤΡΘ–Ά≤Μ±Ί Ι”ΟœύΆ§ΒΡ”ο―‘ΓΘΡζΫΪ–η“Σ Ι”Ο≤β ‘ΤΫΧ®…ζ≥…”ο―‘±ύ–¥ΑϋΉΑΡΘΩιΘ§“‘ΤδΥϊ”ο―‘ ΒάΐΜ·ΡΘ–ΆΓΘΡζΜΙΫΪ–η“ΣΕύ”ο―‘ΡΘΡβΤςά¥±ύ“κΚΆΒς ‘…ηΦΤΓΘ

·‘Ύ≤Ϋ÷η1÷–Θ§¥¥Ϋ®œνΡΩ ±Θ§ΫΪ”ο―‘…η÷ΟΈΣΫΪ…ζ≥…≤β ‘ΤΫΧ®ΒΡ”ο―‘ΓΘΜΙΫΪΡΘΡβΤς…η÷ΟΈΣΕύ”ο―‘ΡΘΡβΤςΒΡΟϊ≥ΤΓΘ

· Ι”Ο≤β ‘ΤΫΧ®”ο―‘¥¥Ϋ®“ΜΗωΑϋΚ§ΑϋΉΑΡΘΩιΒΡ–¬ΈΡΦΰΘ§ΗΟΈΡΦΰΩ… ΒάΐΜ·…ηΦΤΡΘ–Ά≤Δ‘ΎΝΫ÷÷≤ΜΆ§”ο―‘÷°Φδ”≥…δ–≈Κ≈άύ–ΆΓΘ…ηΦΤΡΘΩι ΒάΐΜ·ΒΡ”οΖ®ΫΪ”…ΡζΒΡΡΘΡβΤς÷ΗΕ®ΓΘΑϋΉΑΤςΒΡΕΥΩΎΫΪ «≤β ‘Χ®«ΐΕ·ΚΆΙέ≤λΒΡ–≈Κ≈ΓΘ

·»γ…œΥυ ωΘ§ΫΪ…ηΦΤΈΡΦΰΧμΦ”ΒΫ“”ΟΜß‘¥ΈΡΦΰ”ΈΡΦΰΦ–÷–ΓΘTestBencherΩ…“‘ΫβΈωVHDLΚΆVerilogΈΡΦΰΘ§“≤Ω…“‘ΫΪΈΡΦΰΖΔΥΆΒΫΕύ”ο―‘ΡΘΡβΤςΓΘ

»ΐΓΔΫΪΕΥΩΎΧα»ΓΒΫΡΘΑεΆΦ÷–

Β±TestBencher¥¥Ϋ®œνΡΩ ±Θ§ΥϋΜΙΜα…ζ≥…“ΜΗωΡΘΑεΆΦΓΘ–¬ΒΡ ¬ΈώΆΦΫΪΑϋΚ§”κΡΘΑεΆΦœύΆ§ΒΡ–≈Κ≈Θ§≤®–ΈΘ§≤Έ ΐΚΆ τ–‘ΓΘ‘Ύ¥¥Ϋ®Ε® ± ¬Έώ÷°«ΑΘ§œ»…η÷ΟΡΘΑεΆΦ «“ΜΗωΚΟ÷ς“βΘ§’β―υΥυ”–Ε® ± ¬ΈώΕΦΫΪΨΏ”–œύΆ§ΒΡΫ”ΩΎ–≈Κ≈ΓΘ

¥ρΩΣΡΘΑεΆΦΘΚ

·‘Ύ“œνΡΩ”¥ΑΩΎ÷–ΒΡ“ΡΘΑεΆΦ”ΈΡΦΰΦ–œ¬Θ§ΥΪΜςΟϊΈΣprojectname_templateDiagram.btimΒΡΆΦ“‘¥ρΩΣΡΘΑεΆΦ¥ΑΩΎΓΘ

·»γΙϊ‘ΎœνΡΩ¥¥Ϋ®≤Ϋ÷η÷–¥¥Ϋ®ΝΥΡ§»œ ±÷”Θ§‘ρΡΘΑεΆΦΫΪΑϋΚ§ΗΟ ±÷”ΉςΈΣ δ»κ–≈Κ≈Θ§≤Δ«“ΜΙΫΪ¥φ‘Ύ“ΜΗω ±÷”…ζ≥…ΤςΆΦΘ§Τδ÷–ΫΪΗΟ ±÷”ΉςΈΣ δ≥ωΓΘ ±÷””ΠΫω”…“ΜΗωΕ® ± ¬Έώ«ΐΕ·Θ§“‘±ψΩ…“‘‘ΎΡΘΡβΫα χ ± Β±ΒΊ÷–÷Ι ±÷”ΓΘ

ΫΪMUTΒΡΕΥΩΎΧα»ΓΒΫΡΘΑεΆΦ÷–ΘΚ

·ΒΞΜς“¥”MUTΧα»ΓΕΥΩΎ”Α¥≈Ξ“‘ΙΙΫ®MUTΘ§≤ΔΫΪMUTΕΥΩΎΒΡ–≈Κ≈≤ε»κΡΘΑεΆΦ÷–ΓΘ

·άΕ…ΪΆΦ±ξ÷Η Ψ–≈Κ≈ΒΡΖΫœρΓΘ”Ο σ±ξ–ϋΆΘ‘ΎΖΫœρΆΦ±ξ…œΘ§ΙΛΨΏΧα ΨΜαΗφΥΏΡζΟΩΗωΆΦœώΒΡΚ§“εΓΘ

·Ρ§»œ«ιΩωœ¬Θ§TestBencher¥”ΕΞΦΕΡΘ–Ά÷–Χα»ΓΕΥΩΎΘ®Έ¥‘ΎΤδΥϊΡΘ–Ά÷– ΒάΐΜ·ΒΡΕΥΩΎΘ©ΓΘ

· Ή¥ΈΙΙΫ®ΚσΘ§Ω…“‘―Γ‘ώ”“ΦϋΒΞΜςΤδΥϊΡΘΩιΘ§»ΜΚσ―Γ‘ώ“…η÷ΟΈΣ≤β ‘÷–ΒΡΡΘ–Ά”“‘ΩΊ÷Τ‘Ύ≤β ‘Χ®÷– ΒάΐΜ·ΡΡ–©ΡΘ–ΆΓΘ

·«κΉΔ“βΘ§”ΟΜß‘¥ΈΡΦΰ¥χ”–¬Χ…ΪΒΡΗ¥―Γ±ξΦ«Θ§±μ ΨΥϋΟ«“―ΙΙΫ®ΓΘ

·ΥΪΜς»ΈΚΈΉιΦΰΫΪ¥ρΩΣ“ΜΗωΙωΕ·ΒΫ¥ζ¬κ÷–ΗΟΈΜ÷ΟΒΡ±ύΦ≠ΤςΓΘ

·ΧμΦ”“Σ‘ΎΥυ”–≤β ‘Χ® ¬Έώ÷–œ‘ ΨΒΡΤδΥϊΆΦ–ΈΕ‘œσΘ§Ϋα χΆΦ±ξΦ«ΚΆ±δΝΩΓΘ

·―Γ‘ώ“ΈΡΦΰ”>“±Θ¥φ ±–ρΆΦ”“‘±Θ¥φΡΘΑεΆΦΓΘ

ΥΡΓΔ¥¥Ϋ®Ε® ±ΫΜ“ΉΤςΆΦ

ΥΡΓΔ¥¥Ϋ®Ε® ±ΫΜ“ΉΤςΆΦ

TestBencherΈΣœνΡΩ÷–ΒΡΟΩΗω ±–ρΆΦ…ζ≥…“ΜΗω ¬Έώ¥Πάμ≥Χ–ρΘ§ΗΟ ¬Έώ¥Πάμ≥Χ–ρ¥ζ±μΡζ’ΐ‘Ύ¥¥Ϋ®ΒΡΉήœΏΙΠΡήΡΘ–ΆΒΡΩ…÷Ί”ΟΫ”ΩΎΙφΖΕΘ®άΐ»γΘ§ΕΝ»Γ÷ήΤΎΘ§–¥»κ÷ήΤΎΘ§÷–Εœ÷ήΤΎΘ©ΓΘ’β–© ¬Έώ¥Πάμ≥Χ–ρ «VerilogΒΡΡΘΩιΘ§VHDLΒΡ ΒΧε/ΧεœΒΫαΙΙΕ‘ΚΆTestBuilderΒΡάύΓΘ≤ΜΙή Ι”ΟΡΡ÷÷”ο―‘Θ§ ¬Έώ¥Πάμ≥Χ–ρΕΦ Ι”ΟœύΆ§ΒΡΆ®”ΟΧεœΒΫαΙΙΓΘ≤Δ«“‘ΎΥυ”–”ο―‘÷–Θ§ ¬Έώ¥Πάμ≥Χ–ρΕΦΨΏ”–άύΥΤΒΡΙΠΡή–‘APIΘ§Ω…”Ο”Ύ¥ΞΖΔΥϋΟ«Θ®ΆΦ±μ”Π”ΟΒς”ΟΘ©ΓΘΫΧ≥ΧΚΆΒΎ2-6’¬Ϋι…ήΝΥ»γΚΈΜφ÷Τ ±–ρΆΦΚΆΩΊ÷Τ…ζ≥…ΒΡ¥ζ¬κΓΘ¥¥Ϋ®–¬ΒΡ ±–ρΆΦ ±Θ§ΥϋΫΪΑϋΚ§ΡΘΑεΆΦΒΡΥυ”––≈Κ≈ΚΆ τ–‘ΓΘΕ‘“Σ‘Ύ≤β ‘Χ®÷–Βς”ΟΒΡΟΩΗωΕ® ±ΫΜ“ΉΤς÷¥––“‘œ¬≤Ϋ÷ηΘΚ

¥¥Ϋ®“ΜΗω–¬ΒΡΕ® ± ¬Έώ¥Πάμ≥Χ–ρΘΚ

·‘Ύ“œνΡΩ”¥ΑΩΎ÷–Θ§”“ΦϋΒΞΜς“ ¬ΈώΆΦ”ΈΡΦΰΦ–Θ§»ΜΚσ―Γ‘ώ“¥¥Ϋ®–¬... ¬Έώ¥ΠάμΤς”≤ΥΒΞ÷°“ΜΓΘ’βΫΪ¥ρΩΣ“ΜΗωΈΡΦΰΕ‘ΜΑΩρΘ§”Ο”Ύ¥¥Ϋ®ΚΆ±Θ¥φΗΟΆΦΓΘ

·±Θ¥φΆΦ±μΚσΘ§ΫΪΤδΧμΦ”ΒΫ“ ¬ΈώΆΦ±μ”ΈΡΦΰΦ–÷–ΓΘΗΟΆΦΫΪΑϋΚ§ΡΘΑε–≈Κ≈ΚΆ τ–‘ΓΘ

÷ς ¬ΈώΤς «‘Υ––“Μ¥Έ»ΜΚσΆΘ÷ΙΒΡ ¬ΈώΘ§”…≤®–ΈΆΦ±ξ±μ ΨΓΘ

¥” τ ¬ΈώΤς «ΫΪΝ§–χ―≠ΜΖ÷±ΒΫ ’ΒΫ÷–÷ΙΒς”ΟΒΡ ¬ΈώΘ§≤ΔΆ®Ιΐ¥χ”–≤®–ΈΚΆΜΖΜΊœΏΒΡΆΦ±ξœ‘ ΨΓΘ¥” ¬ΈώΆ®≥Θ‘Ύ≤β ‘ΤΫΧ®ΒΡΩΣ Φ¥ΠΩΣ ΦΘ§“Μ÷±‘Υ––ΒΫ≤β ‘ΤΫΧ®Άξ≥…ΈΣ÷ΙΓΘ

· Ι”Ο ±–ρΆΦ±ύΦ≠ΤςΆ®ΙΐΜφ÷Τ≤®–Έά¥¥¥Ϋ® ±–ρΆΦΓΘΩ…―ΓΕ‘œσΘ®άΐ»γ―υ±ΨΘ§±ξΦ«Θ§―”≥ΌΘ§±δΝΩΚΆάύΖΫΖ®Θ©ΫΪ‘Ύ±Ψ ÷≤αΒΡΚσΟφ≤ΩΖ÷Ϋχ––œξœΗΧ÷¬έΘ§≤Δ‘ΎΫΧ≥Χ÷–Ϋχ––―ί ΨΓΘ”–ΙΊ»γΚΈ¥¥Ϋ® ¬ΈώΒΡ–≈œΔΘ§«κ≤ΈΦϊΒΎ2-6’¬ΓΘ

·―Γ‘ώΈΡΦΰ>±Θ¥φ ±–ρΆΦ≤ΥΒΞ―Γœν“‘±Θ¥φ ±–ρΆΦ≤Δ…ζ≥…HDL¥ζ¬κΓΘΟΩ¥Έ±Θ¥φ ±–ρΆΦ ±Θ§ΕΦΜαΈΣΤδ…ζ≥…–¬¥ζ¬κΓΘ

«–ΜΜΒΫ¥”’ΨΚΆ÷ς’ΨΘΚ

±–ρΆΦΒΡ“¥”Μζ”ΚΆ“÷ςΜζ”…η÷ΟΜα”ΑœλΈΣ ±–ρ ¬Έώ…ζ≥…¥ζ¬κΒΡΖΫ ΫΓΘ¥¥Ϋ® ±–ρΆΦΚσΘ§ΡζΩ…“‘Ά®Ιΐ÷¥––“‘œ¬≤ΌΉςΗϋΗΡΈΣΤδΥϊ…η÷ΟΘΚ

·‘Ύ“œνΡΩ”¥ΑΩΎ÷–”“ΦϋΒΞΜς ±–ρΆΦΟϊ≥ΤΘ§»ΜΚσ¥”…œœ¬ΈΡ≤ΥΒΞ÷–―Γ‘ώ“ΆΦ…η÷Ο”“‘¥ρΩΣ“ΆΦ…η÷Ο”Ε‘ΜΑΩρΓΘ

·»ΜΚσΦλ≤ι“¥” τ ¬Έώ¥Πάμ”Μρ“÷ς ¬Έώ¥Πάμ”ΒΞ―ΓΑ¥≈ΞΓΘ

≤ιΩ¥…ζ≥…ΒΡHDL‘¥¥ζ¬κΘΚ

”…”ΎΟΩ¥Έ±Θ¥φ ±ΕΦΜα÷Ί–¬…ζ≥… ±–ρΆΦΒΡ‘¥¥ζ¬κΘ§“ρ¥ΥΡζ≤Μ”ΠΕ‘¥ζ¬κΫχ––»ΈΚΈ ÷Ε·ΗϋΗΡΓΘΒΪ «Θ§”– ±”– ±Ω…“‘ΗυΨίΆΦ÷–ΒΡΫαΙΙά¥ΝΥΫβΒΉ≤ψ¥ζ¬κΒΡ±δΜ·ΖΫ ΫΓΘ

·ΒΞΜς“‘¥¥ζ¬κ”Α¥≈Ξ“‘¥ρΩΣ±ύΦ≠Τς≤Δ≤ιΩ¥¥ζ¬κΓΘ

»μΦΰΈόΖ®œ¬‘ΊΘΩ≤Μ÷ΣΒάΫβ―ΙΟή¬κΘΩΈΔ–≈ΙΊΉΔΕ©‘ΡΚ≈"…ΝΒγœ¬‘Ί"Μώ»Γ

±ΨΧϊ≥ΛΤΎΗϋ–¬Ήν–¬Αφ «κ ’≤Ίœ¬‘ΊΘΓΑφ»®…υΟςΘΚ±Ψ’ΨΧαΒΡ–ρΝ–Κ≈ΓΔΉΔ≤α¬κΓΔΉΔ≤αΜζΓΔΤΤΫβ≤ΙΕΓΒ»Ψυά¥Ή‘ΜΞΝΣΆχΘ§ΫωΙ©―ßœΑΫΜΝς÷°”ΟΘ§«κ‘Ύœ¬‘ΊΚσ24–Γ ±ΡΎ…Ψ≥ΐΓΘ