Xilinx Vivado Design Suite 2024 HLx版为用户带来全新的超高生产力设计方法。使用基于C/C++和IP的设计。新版HLX包括HL系统版本、HL设计版本和HLWebPACKT%版本。结合最新ultraFast“高级生产力设计方法指南,相比采用传统方法而言,用户可将生产力提升10-15倍。其优势在于基于C/C++的设计和加速复用,拥有特定领域专用库,IP子系统和集成自动化,加速设计收敛,实现快速的平合创建与部署,以及面向Zynq SoC和最新MPSOC,以及ASIC级的FPGA和3DIC。让你的生产力直线提升,有别于将大部分设计精力用在设计流程后端的传统RTL设计,基于C语言和IP的设计可缩短验证、实现和设计收敛的开发周期,使设计人员能够集中精力开发差异化逻辑。可快速生成平台连接设计以及必要的软件协议栈。使用高层次设计快速开发差异化逻辑。此外,还能支持广泛的优化设计复用。与RTL相比,可利用高级语言显著缩短验证时间。充分利用高层次抽象功能,设计团队能够快速获得整体同样出色甚至更好的结果质量(性能、功耗和利用率)。HLx不仅能够加速创建、设计修改和复用,而且还可提供相应方法用于设计具有软件可编程的自定义平台,进一步配合补充赛灵思SDx系列软件定义环境。将平台开发与差异化逻辑分离,使设计人员专注于实现公司的高价值功能。利用具有开发板感知功能的Vivado IP集成器(IPI)以及Vivado IP系统,快速完成平台连接设计的配置、生成和收敛。为差异化逻辑实施基于C语言的仿真,与传统RTL仿真相比,仿真时间可显著缩短。利用Vivado HLS和C/C++库进行高层次综合,并通过IPIntegrator执行从C到芯片的快速实现与系统集成。当开发衍生设计时,还能大幅提升生产力。调整不同器件、时钟速度或设计配置就像编辑C参数或 Vivado HLS选项一样简单。然后,工具会自动选择可满足新产品要求的新的微架构。本次带来最新破解版,含授权文件,亲测可完美破解激活软件,专业软件,超级的大,安装比较久,但是破解起来非常简单!

Vivado 设计套件是 Xilinx 为设计、综合和分析 HDL 的软件套件,用于其 FPGA 和 SoC 系列。Vivado Design Suite包括许多工具,如Vivado,Vitis,Vitis HLS和许多其他工具。

Vivado 设计套件提供了多种方法来完成 Xilinx FPGA 设计和验证中涉及的任务。除了传统的 RTL 到比特流 FPGA 设计流程外,Vivado 设计套件还提供了新的系统级集成流程,专注于以 IP 为中心的设计。在流程的每个阶段启用设计分析和验证。设计分析功能包括逻辑仿真、I/O 和时钟规划、功耗分析、时序分析、设计规则检查 (DRC)、设计逻辑和实现结果的可视化以及编程和调试。

整个解决方案集成在称为 Vivado 集成设计环境 (IDE) 的图形用户界面 (GUI) 中。Vivado IDE 提供了一个接口,用于组装、实现和验证设计和 IP。此外,所有流程都可以使用 Tcl 应用程序编程接口 (API) 运行。可以使用 Tcl 提示符以交互方式输入 Tcl 命令,也可以将其保存在 Tcl 脚本中。您可以使用 Tcl 脚本运行整个设计流程,包括设计分析,或者只运行部分流程

新版说明

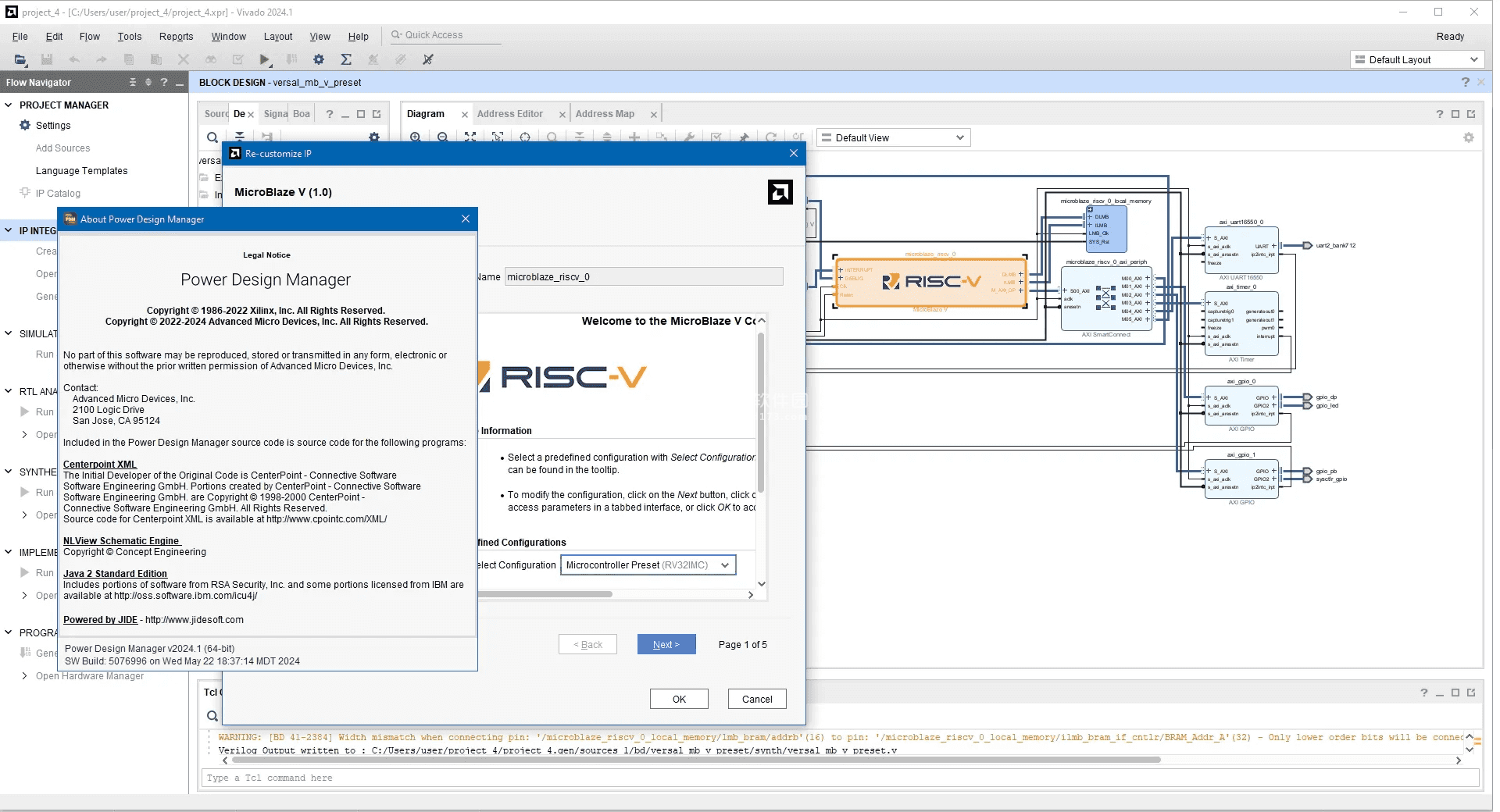

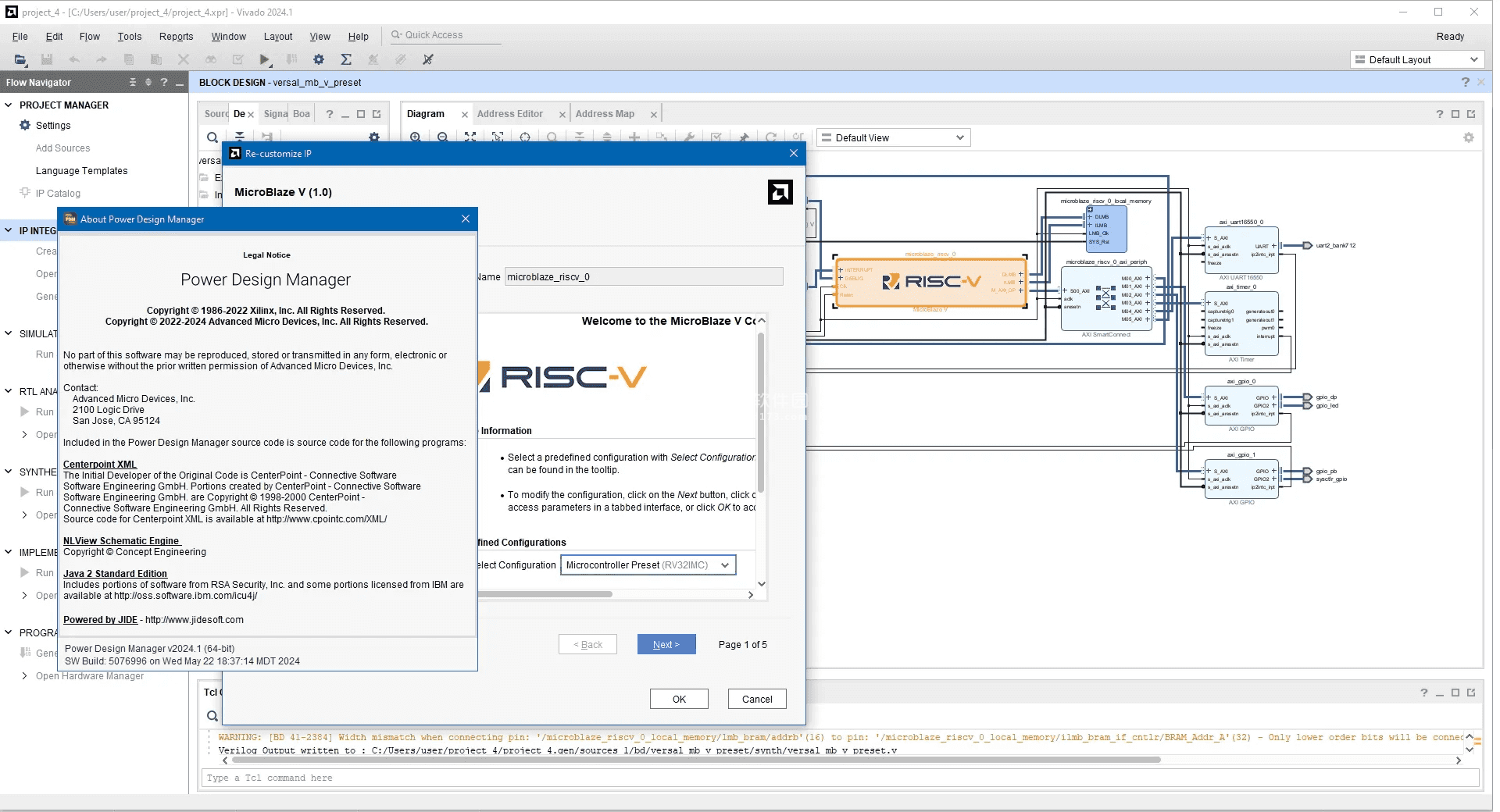

Vivado 2024.1 新增功能 - 日期:2024

年 5 月 30 日 MicroBlaze V 软处理器的通用访问(基于 RISC V 开源 ISA)

Versal 器件的 QoR (FMAX) 增强功能 - 跨 SLR 边界优化时钟和 P&R(适用于多单反 Versal 设备)

- 物理优化

期间用户控制的重定时

- 用户控制时钟树选择,可将时钟偏移降至最低

动态函数交换 (DFX) 增强功能

- 增强了 DFX 设计报告,以帮助完成设计收敛

- 增加了对串联配置和针对 DFX 的支持 Versal SSIT 器件,以满足 PCIe 时序要求

时序要求

Power Design Manager

- 添加了对 Zynq UltraScale+ RFSoC 器件

的支持- 分类片上功率和静态电流

图表 - 能够将 PDM 表格复制并导出到电子表格,以便快速共享信息

年 5 月 30 日 MicroBlaze V 软处理器的通用访问(基于 RISC V 开源 ISA)

Versal 器件的 QoR (FMAX) 增强功能 - 跨 SLR 边界优化时钟和 P&R(适用于多单反 Versal 设备)

- 物理优化

期间用户控制的重定时

- 用户控制时钟树选择,可将时钟偏移降至最低

动态函数交换 (DFX) 增强功能

- 增强了 DFX 设计报告,以帮助完成设计收敛

- 增加了对串联配置和针对 DFX 的支持 Versal SSIT 器件,以满足 PCIe

时序要求

时序要求Power Design Manager

- 添加了对 Zynq UltraScale+ RFSoC 器件

的支持- 分类片上功率和静态电流

图表 - 能够将 PDM 表格复制并导出到电子表格,以便快速共享信息

软件特色

1、加速高层次设计

软件定义 IP 生成 - Vivado 高层次综合 (HLS)

基于模块的 IP 集成,包含 Vivado IP Integrator

基于模型的设计,集成 Model Composer and System Generator for DSP

2、加速验证

Vivado 逻辑仿真器

集成混合语言仿真器

集成 & 独立编程与调试环境

加速验证超过 100 倍,通过 C、 C++ 或 SystemC 以及 Vivado HLS

验证 IP

3、加速实现

设计实现时间缩短 4 倍

设计密度提升 20%

在低端 & 中档产品中实现高达 3 速度级性能优势,在高端产品中实现 35% 功耗优势

软件功能

1、突破器件密度极限:在单个器件中更快速集成更多功能。

如果设计工具能够让All Programmable器件集成更多功能,用户就能够为系统设计选择尽可能小的器件,从而直接带来系统成本和功耗的下降。Vivado设计套件提供一种集成环境,能够让架构、软件和硬件开发人员在通用设计环境中协作工作,从而最大程度地提升设计效率,充分发挥Al Programmable器件的可编程逻辑架构及其专用片上功能模块的潜力。

2、Vivado以可预测的结果提供稳健可靠的性能和低功耗出于纳米级IC设计的物理原因,互联已经成为28nm及更高工艺节点的可编程逻辑器件架构的性能瓶颈。Vivado设计套件采用先进的布局布线算法,可突破该性能瓶颈,而且点击鼠标即可得到高性能结果。

Vivado设计套件的分析型布局布线算法能够同步优化包括时序、互联使用和走线长度在内的多重变量,提供可预测的设计收敛。同时,Vivado的实现引擎可保证在逻辑利用率高的大型器件上得到的结果和在器件利用率较低的设计上得到的结果一样优异。此外,在系统设计规模随着系统功能的增加而逐步增大的情况下,Vivado既能保持高性能结果,还能提高各次运行结果间的一致性。

3、Vivado设计套件提供无与伦比的运行时间和存储器利用率从设计人员生产力考虑,设计工具应能够快速运行,最好是快到每天能够完成多次编译,这样设计团队就能够迅速得到最终设计。从一开始Vivado设计套件就是为高速运行设计的,比同类竞争的可编程逻辑设计工具的速度明显要快得多。

4、使用Vivado高层次综合生成基于C语雷的IP如今的无线、医疗、军用和消费类应用均比以往更加尖端,使用的算法也比以往更加复杂。业界算法开发的金标准就是采用C、C++和SystemC高级编程语言。过去设计流程中需要经过一个缓慢且容易出错的步骤来捋用C、C++或SystemC语言编写的算法转换为适合于综合的Verilog或VHDL硬件描述。而现在Vivado设计套件系统版本中提供的Vivado高层次综合功能可轻松地自动完成这一步骤。

您以往可能听说过C语言级硬件综合。不管您听说过什么,C语言级算法综合已成为系统级设计的捷径。当前有超过400名用户正在成功利用Vivado高层次综合(HLS)技术开发符合C、C++和SystemC语言规范的赛灵思All Programmable器件用IP硬核。

Vivado HLS通过下列功能,让系统和设计架构师走上IP硬核开发的捷径:

·算法描述、数据类型规格(整数、定点或浮点)和接口(FIFO、AX14、AXI4-Lite、AX14-Stream)

抽象化;

·采用可提供最佳QoR(结果质量)的基于指合的架构感知型编译器;

·使用C/C++测试平台仿真、自动化VHDL/Verilog仿真和测试台生成功能加快模块级验证;

·发挥整套Vivado设计套件的功能,捋生成的IP硬核轻松嵌入基于RTL的设计流程中;发挥Vivado System Generator for DSP的功能,将生成的IP硬核轻松嵌入基于模型的设计;发挥Vivado IP集成器(Vivado IPIntegrator)的功能,将生成的IP硬核轻松集成到基于模块的设计。

这样硬件设计人员就有更多时间投入到设计领域的探索中,即有更多时间评估备选架构,找出真正理想的设计解决方案,轻松应对各种严峻的系统设计挑战。例如设计人员将行业标准的浮点math.h运算与Vivado HLS结合使用,就能够在实现较手动编码的RTL更优异的QoR的同时,让线性代数算法的执行速度呈数量级提高(10倍)

5、利用System Generator for DSP实现基于模块的DSP设计集成

如上文所述,Vivado设计套件系统版本提供System Generator for DSP,这是一款行业领先的捋DSP算法转换为高性能生产质量级硬件的高级设计工具,转换所需时间仅为传统RTL设计方法的几分之一。

Vivado System Generator for DSP可让开发人员运用业界最高级的All Programmable系统建模工具(MathWorks@提供的SimulinkTM和MATLABTM),无缝集成那些可用Vivado HLS综合到硬件中的算术函数、SmartCORETM与LogiCORETM IP、定制RTL以及基于C语言的模块,从而加速高度并行系统的开发。

使用Vivado HLS和Vivado System Generator for DSP将基于C语言的模块集成到Simulink中的设计流程。

Vivado System Generator for DSP提供自动定点/浮点硬件生成功能、可将Simulink仿真速度提高1000倍的硬件协同仿真功能、用于基于RTL的Vivdo设计流程的系统集成功能,以及用Vivado IP集成器实现的基于模块的设计功能,可进一步加快系统实现。

6、利用Vivado IP集成器实现基于模块的IP集成

Vivado设计套件提供行业首款即插即用IP集成设计环境Vivado IP集成器,打破了RTL设计生产力的局限性。

Vivado IP集成器提供图形化、脚本编写(Tcl)、生成即保证正确(correct-by-construction)的设计开发流程。此外,它还提供具有器件和平台意识的环境,以及强大的集成调试功能,能支持主要IP接口的智能自动连接、一键式IP子系统生成、实时设计规则检查(DRC)和接口修改传递等。

设计人员在使用Vivado IP集成器建立IP模块之间的连接时,工作在抽象的“接口”层面而非“信号”

层面。抽象上升到接口层面显著提高设计人员的生产力。虽然主要使用的是业界标准的AX14接口,IP集成器也支持数十种其他常用接口。

7、用于设计和仿真的Vivado集成设计环境

Vivado设计套件还提供完整的全集成成套工具,用于在先进的集成设计环境(IDE)中完成设计输人、时序分析、硬件调试和仿真工作。Vivado设计套件的集成设计环境的这种设计分析功能采用共享的可扩展数据模型,以容纳超大型All Programmable器件。Vivado设计套件在整个设计流程中使用这一单一的数据模型,让设计团队能够尽早在整个设计流程中随时掌握时序、功耗、资源利用率、路由拥塞等关键设计指标。估算也会随着设计流程的推进越来越准确,从而在减少设计迭代次数的同时推动更快完成设计收敛。

Vivado设计套件是唯一在自身的集成设计环境中提供混合语言仿真器的设计解决方案。就同类竞争仿真器而言,用户必须或选择VHDL仿真,或选择Verilog仿真。

对集成众多厂商提供的IP的最新系统设计来说,混合语言仿真器至关重要。

Vivado设计套件的仿真和调试使用相同的波形观测仪,这样可以避免从仿真环境切换到硬件调试环境后还需要重新学习。竞争解决方案往往迫使用户学习和使用不同波形的工具来完成相同工作。在仿真功能和调试功能全集成的情况下,设计团队能够更快地完成工作,且避免出错,使用Vivado设计套件就是这种情况。

类似地,同类竞争开发工具的交叉探测功能呈碎片化且极度有限。此外这些交叉探测功能一般局限于某种单一的工具。与此对比鲜明的是,Vivado设计套件提供的全面、集成式front-to-back交叉探测功能,适用于所有不同设计视图,诸如实现设计、综合设计、时序报告,甚至还可追溯到设计团队的原始RTL代码。

由于Vivado设计套件使用单一数据模型架构,所以可在各种设计资源、原理图视图、层级浏览器、设计报告、消息、布局规划和Vivado器件编辑器(Vivado Device Editor)之间进行大范围交叉探测。借助这种独特的功能,可以即时反馈整个系统开发过程中发现的任何设计问题,,从而加快调试,快速完成时序收敛。此外,竞争性设计解决方案使用多个磁盘文件用于工具间通信。使用多个磁盘文件带来的复杂性和低效率不仅会降低工具性能,而且还会造成多重接口,从而显著增大工具间沟通不畅的几率。然而,Vivado设计套件则不存在这种问题。它采用单一的共享数据模型处理设计的各方面工作

8、综合而全面的硬件调试

Vivado设计套件的探测方法直观、灵活、可重复。设计人员可选择最适合自己设计流程的探测策略:

·RTL设计文件、综合设计和XDC约束文件

·网表插入

·用于自动运行探测的互动式TCL或脚本

先进的触发器和采集功能:

Vivado设计套件为检测复杂事件提供先进的触发器和采集功能。在调试进程中所有的触发器参数均可使用,用户可以实时检查或动态修改参数,且无需重新编译设计。

Zymq SoC支持处理器系统(PS)与可输程逻辑(PL)之间交叉触发Vivado设计套件还支持Zyng-7000All Programmable SoC器件内处理器系统(PS)与可编程逻辑(PL)之间的交叉触发。有了这项功能,结合使用赛灵思软件开发套件(SDK)、Vivado IP集成器和Vivado逻辑分析器(Vivado Logic Analyzer),可以协同调试同时使用Zynq处理器系统和可编程逻辑的嵌入式设计。再搭配强大的软件调试器GNU Debugger(GDB)实用工具,设计人员使用Vivado IP集成器和Vivado逻辑分析器可以同步调试软/硬件算法。Zynq-7000All Programmable SoC平台和赛灵思ILA

(集成逻辑分析器)IP核间提供有特定的接口信号,可支持无缝协同调试操作。

实现硬件实时读/写操作-JTAG to AXI Master:

Vivado设计套件可在硬件调试过程中实时地完成Zynq处理器系统和可编程逻辑间的读/写事务处理。最新调试IP核(JTAG to AXI Master)与简便易用的IPIntegrator流相结合,能够在设计中访问任何基于AXI的IP模块中的数据。

优势包括:

·在设计过程中,能够在外设上完成简单的读/写操作

·无需重新编译就能将测试模式写入存储器

·通过AXI接口能够测试和校正IP核·能够检查任何AlX外设设备内的数据

集成串行/O分析器:

Vivado串行I/0分析器为基于FPGA的系统设计中日渐常用的高速串行I/O通道提供了一种快速、便捷的互动式设置调试方法。Vivado串行I/0分析器能够在串行I/O通道运行期间对多种高速串行1/O通道进行误码率(BER)测试,并实时调整高速串行收发器的参数。这款基于链路的Vivado串行1/0分析器,能够将系统中任何收发器的发射器(TX)连接到任何收发器的接收器(TX)。此外发射器和接收器无需采用相同的SerDes架构。Vivado串行I/O分析器还能够自动检测各条链路,让开发人员创建定制链路,执行2D眼图扫描并实时扫描收发器参数。

9、采用C、C++和SystemC语冒将验证速度提高100倍以上

如前文所讨论的,Vivado设计套件系统版本内置Vivado HLS,可帮助用户的设计团队用C、C++

和SystemC语言迅速完成算法设计的创建与迭代工作,同时还在验证工作中发挥这些高级编程语言的高仿真速度优势。使用Vivado HLS定点和业界标准浮点math.h库,开发人员运用C函数规范即可快速为设计建模并完成设计迭代,然后仅根据时钟周期和吞吐量等考虑因素建立目标感知的RTL架构。将C、C++和SystemC语言用作初始设计和建模语言可极大地加快仿真速度(比RTL仿真速度快数千倍)。

在一个视频设计实例中,10个经处理的视频帧的仿真速度采用C语言比采用HDL快12,000倍,如表2所示。

安装破解教程

1、在本站下载并解压,如图所示,得到xsetup.exe是安装程序,crack破解文件夹

2、双击xsetup.exe运行安装软件,如图所示,将三个我接受选项都勾选上,才能点击next

3、如图所示,选择要安装的选项,勾选并点击next,小编这里选择第二项

Vivado HLWebPACK:

Vivado HL WebPACK是Vivado Design Edition的免费,设备限制版本。用户可以选择将Model Composer和System Generator for ISP添加到此安装中。

Vivado HL设计版:

Vivado Ht Desin Edition包括用于设计的全套Vivado Design Suite工具,包括基于C的设计,包括Vivado高级综合,实现,验证和器件编程。包括完整的设备支持,电缆驱动程序和Documentation Wavigator。用户可以选择将Model Composer添加到此安装中。

Vivado HL系统版:

Vivado HL系统版是Vivado Ht设计版的超集,增加了System Generator for DSP。包括完整的设备支持,电缆驱动器和文档llavigator。用户可以选择将Model Composer添加到此安装中。

文档llavigator(独立):

Xilinx文档llavigator(Docllav)可以在Web和桌面上访问Xilinx技术文档。这是一个没有Vivado Desin Suite的独立安装。

4、如图所示,通过选择下面树中的项目来自定义您的安装。 将光标移到下面的选项上可提供其他信息。

Vivado Ht Design Edition包括用于设计的全套Vivado Design Suite工具,包括基于C的设计,包括Vivado高级综合,实现,验证和器件编程。 包括完整的设备支持,电缆驱动程序和Documentation Wavigator。 用户可以选择将Model Composer添加到此安装中。

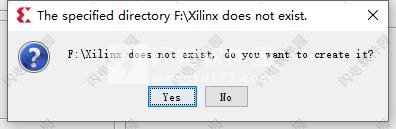

5、这个软件真的是超级的大啊,默认C盘,小编是不够安装的,不过最好还是不要安装在C盘,我们选择一个足够大的磁盘,可直接将C改为 其他磁盘即可,点击next

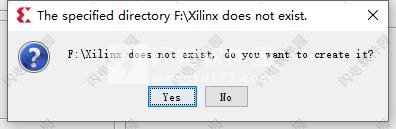

6、提示F:\ Xilinx不存在,你想创建吗?点击yes

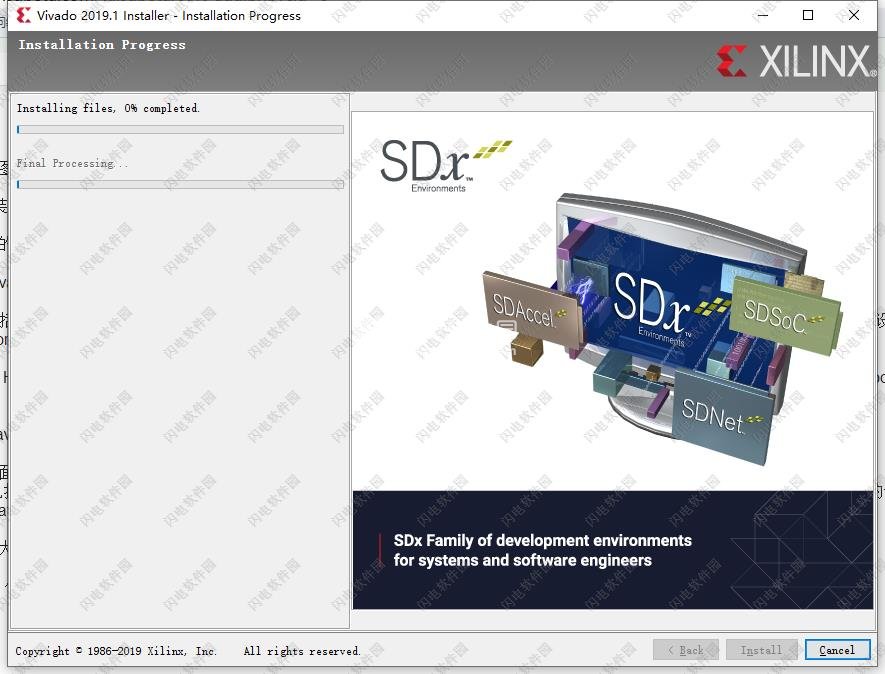

7、点击安装并耐心等待吧,安装时间超级久,大家可以不用留守

8、安装完成后不要运行软件

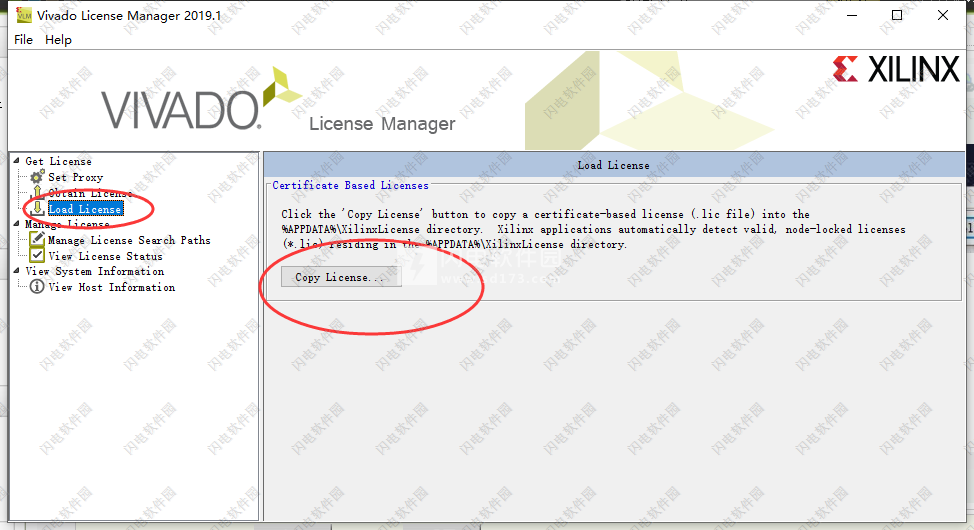

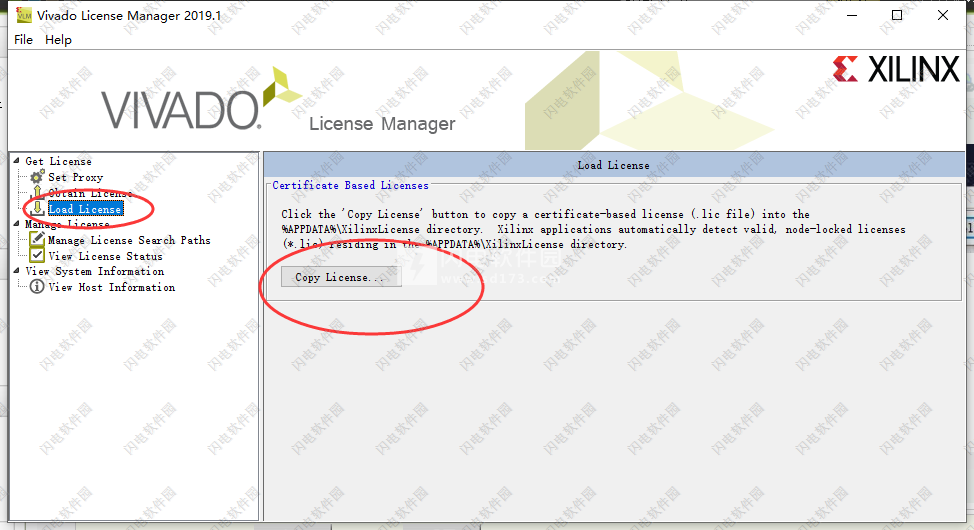

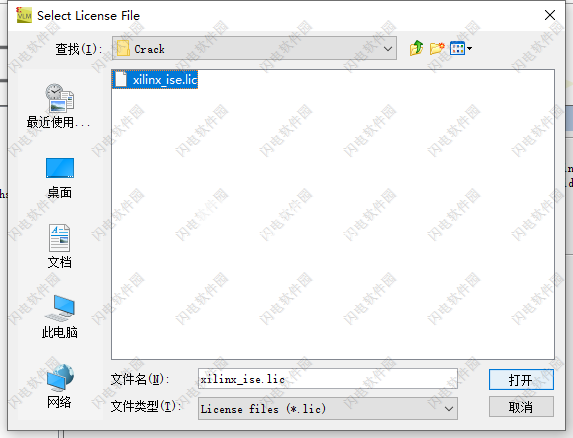

9、在Xilinx License Configuration Manager中,如图所示,点击Copy License选项按钮

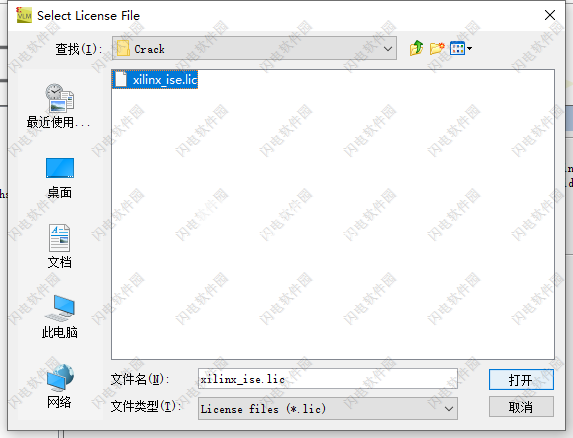

10、然后使用crack破解文件夹中的xilinx_ise.lic即可

使用帮助

一、使用“创建和打包新IP向导”

重要信息:某些Xilinx IP需要许可。 购买所需许可证后,您可以在设计中包含Xilinx IP。

Vivado @集成设计环境(IDE)创建和打包新IP向导允许您创建和打包以下内容:

·使用源文件和Vivado Design Suite项目信息的IP

·框图(BD),XCI和XCIX文件

·来自指定目录的IP

·AX14外围设备的模板,包括:

。 HDL文件

。驱动程序

。测试应用程序

。 示例模板

。 验证IP:有关更多信息,请参阅以下文档:

-AXI验证IP LogiCORE IP产品指南(PG267)[Ref32]

-AXI4-Stream验证IP LogiCORE IP产品指南(PG277)[参考33]

-Zyng-7000 SoC验证IP(DS940)[Ref34]

-Zyng UltraScale + MPSoC验证IP(DS941)[参考35]

Create and Package New IP向导可以生成Xilinx支持的AXI接口。 这些是:

·AX14:用于存储器映射接口,允许在单个地址阶段突发多达256个数据传输周期。

·AXI4-Lite:轻量级,单事务内存映射接口。

·AXI4-Stream:用于高速流数据。

有关Xilinx采用AXI的更多信息,请参阅Vivado设计套件:AXI参考指南(UG1037)[参考资料24]。

注意:出于添加自定义RTL以便在IP集成器中使用的简单目的,可以在Vivado Design Suite用户指南中的此链接中使用模块参考功能:使用IP Integrator设计IP子系统(UG994)[参考文献23]。

二、使用“创建和包IP”向导

从一个开放的Vivado项目,创建和打包新IP向导将带您逐步完成IP创建和打包步骤。 要运行“创建和打包新IP”向导:

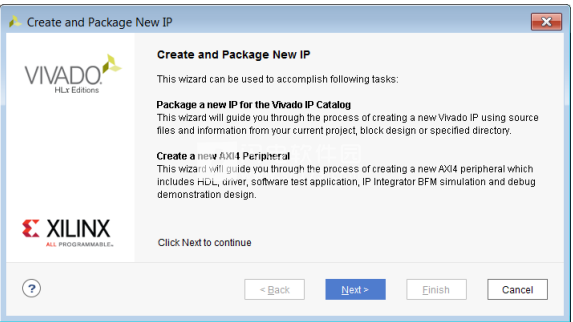

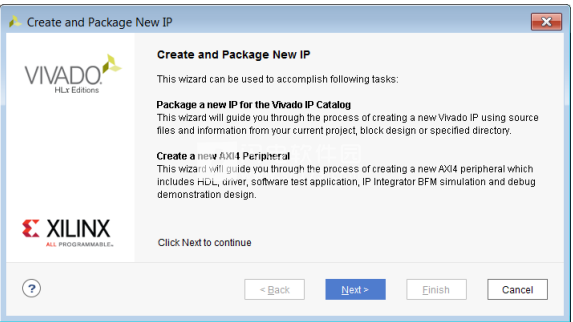

1.从“工具”菜单中,选择“创建和打包新IP”。 将打开Create and Package New IP向导的第一页,如图3-1所示。。

2.使用向导完成以下任务之一:

。 为Vivado IP目录打包一个新IP:指导您使用源文件和当前项目或指定目录中的信息创建新的Vivado IP。

创建新的AX14外设:创建一个新的AXl4外设,包括HDL,驱动程序,测试应用程序和验证IP(VIP)示例模板。

3.单击下一步。

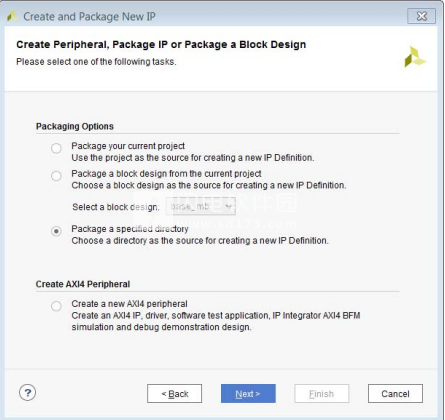

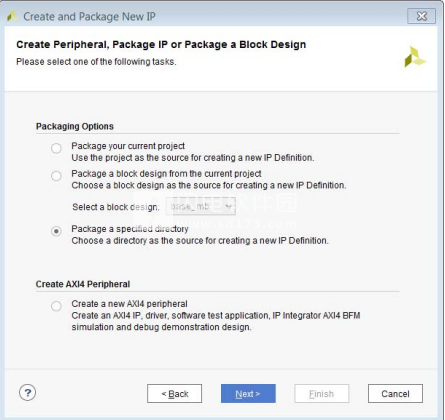

将打开“创建外围设备,包IP或打包块设计”页面,如下图所示。

4.选择以下选项之一:

。包装当前项目:请参阅打包当前项目。

。从当前项目中包装块设计:请参阅打包块设计。

.Package指定目录:请参阅打包指定目录。

。创建一个新的AXl4外设:请参阅创建新的AXl4外设。

5.单击下一步。

根据您选择的“选择创建或包”选项,下一个对话框选项会有所不同。 以下部分描述了这些选项。

根据您选择的“选择创建或包”选项,下一个对话框选项会有所不同。 以下部分描述了这些选项。

软件无法下载?不知道解压密码?微信关注订阅号"闪电下载"获取

本帖长期更新最新版 请收藏下载!版权声明:本站提的序列号、注册码、注册机、破解补丁等均来自互联网,仅供学习交流之用,请在下载后24小时内删除。