АВзАЦЦНтНЬГЬ

Quartus II

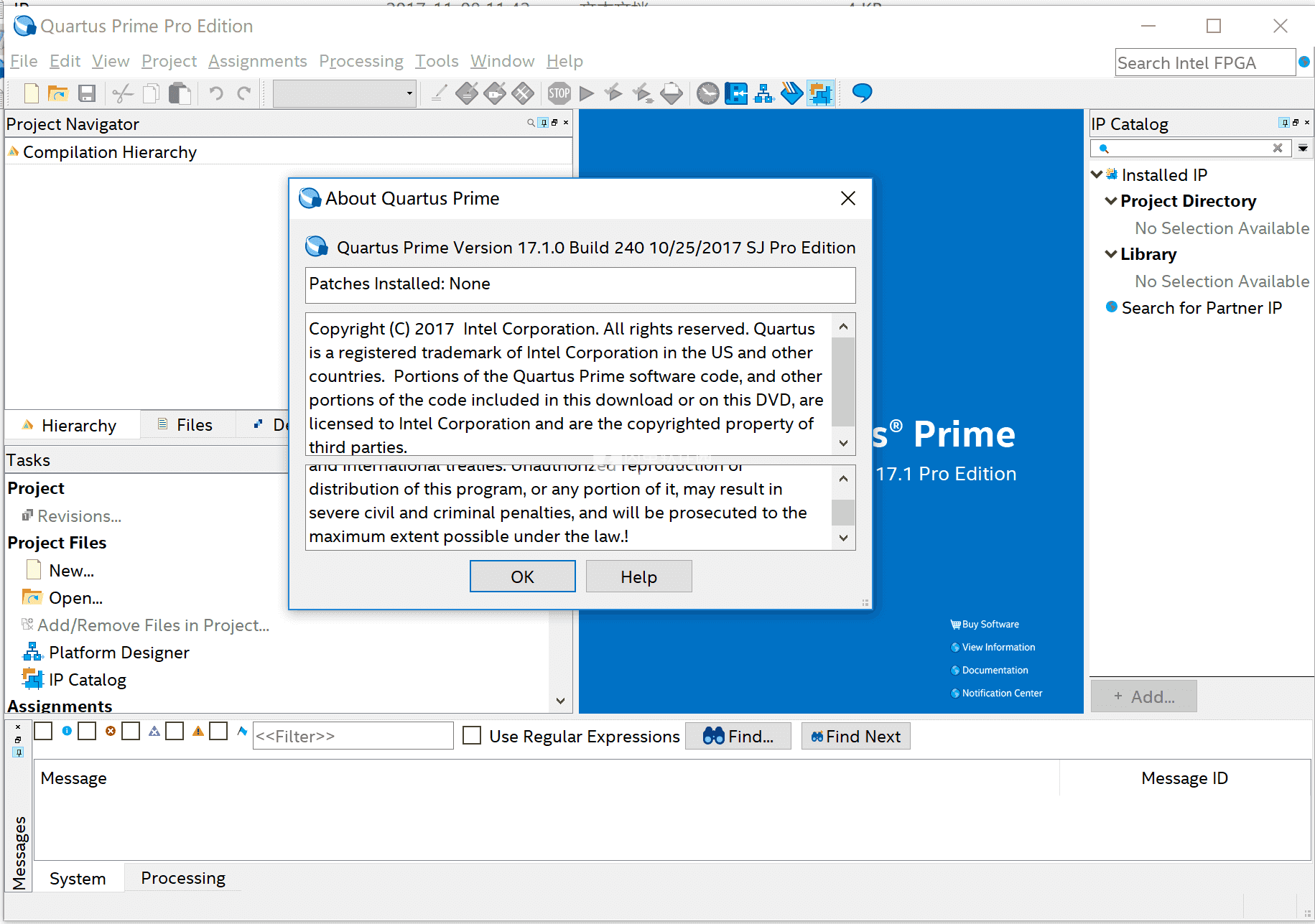

QuartusProSetup-17.1.0.240-windows

дкБОеОЯТдиВЂАВзАШэМўЃЌАВзАЭъГЩКѓЯШВЛвЊЦєЖЏЃЌЕЏГіЕФЦєЖЏНчУцЪБЃЌбЁ“Cancel”ЃЌШчЯТЭМЫљЪО

ЖўЁЂМЄЛю

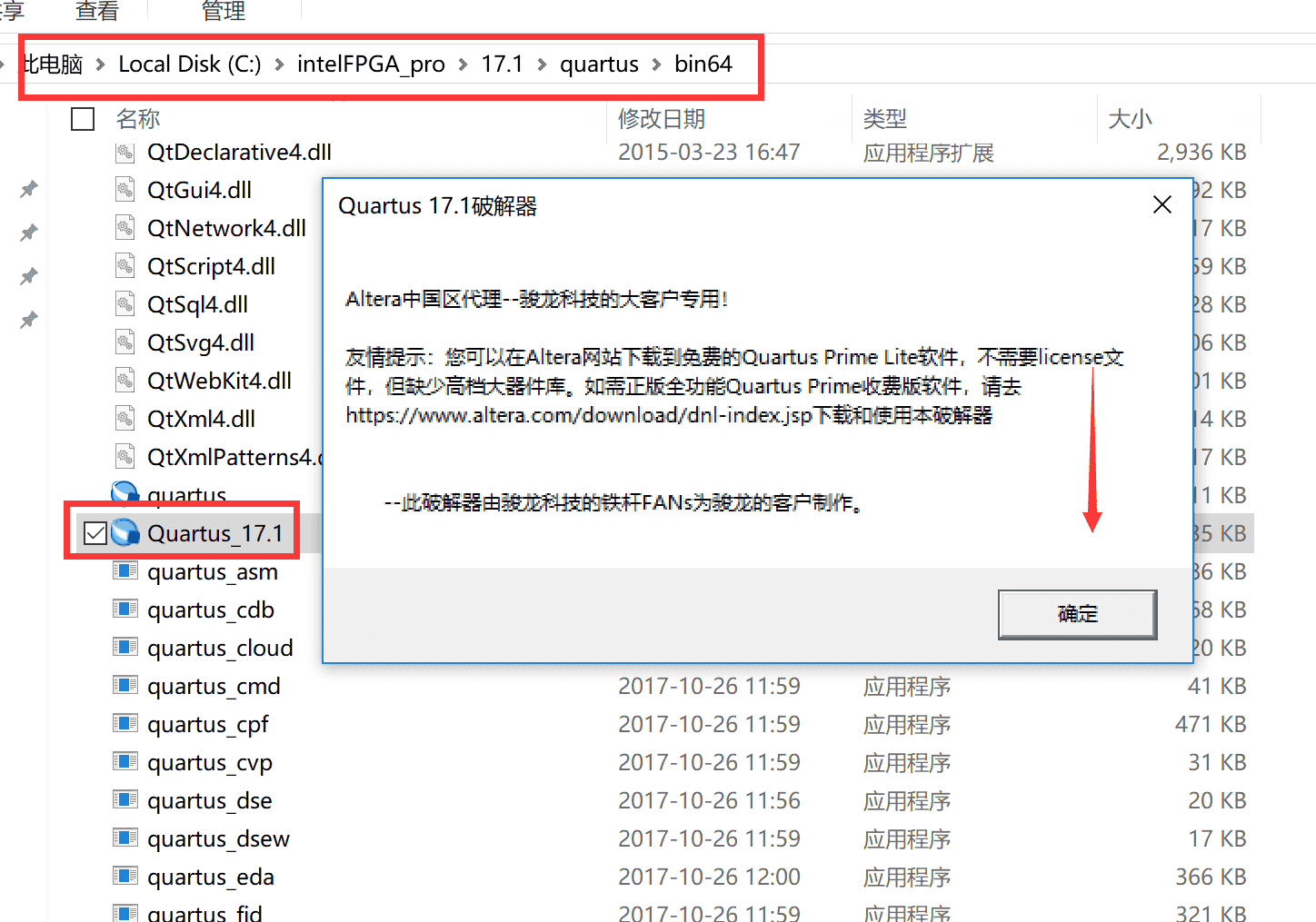

1ЁЂШчЭМЫљЪОЃЌНЋАВзААќжаcrackЮФМўМаФкЕФQuartus_17.1.exeЦЦНтВЙЖЁИДжЦЕНАВзАФПТМжаЃЌЫЋЛїдЫааЃЌШчЭМЫљЪОЃЌЕуЛїШЗЖЈАДХЅ

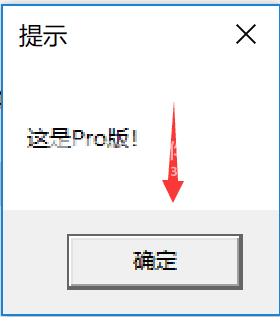

2ЁЂздЖЏЪЖБ№ЪЧproАцЃЌЕуЛїШЗЖЈАДХЅ

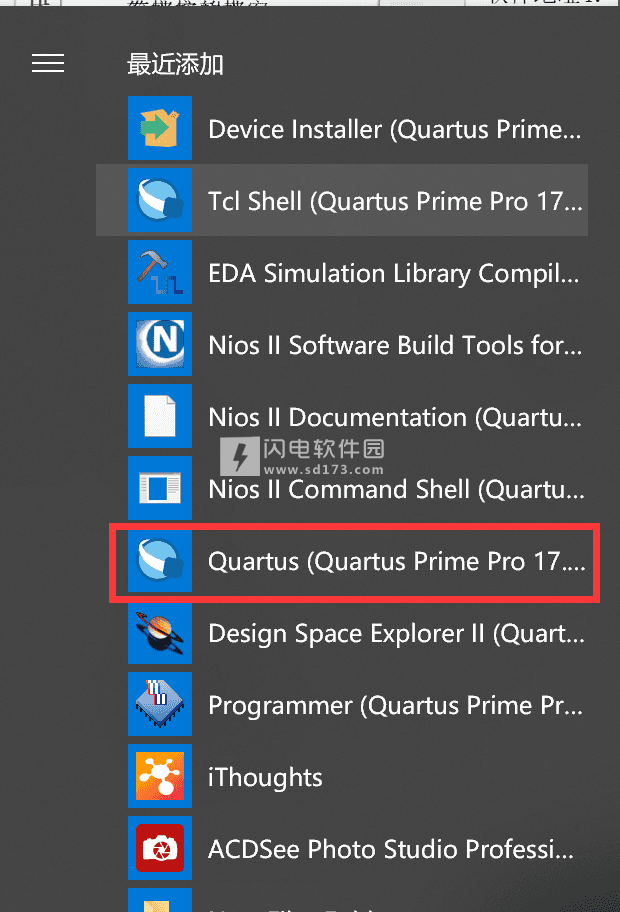

3ЁЂдкПЊЪМВЫЕЅжаевЕНQuartus (Quartus Prime Pro 17.1)ЃЌВЂЕуЛїЦєЖЏЃЌШчЭМЫљЪО

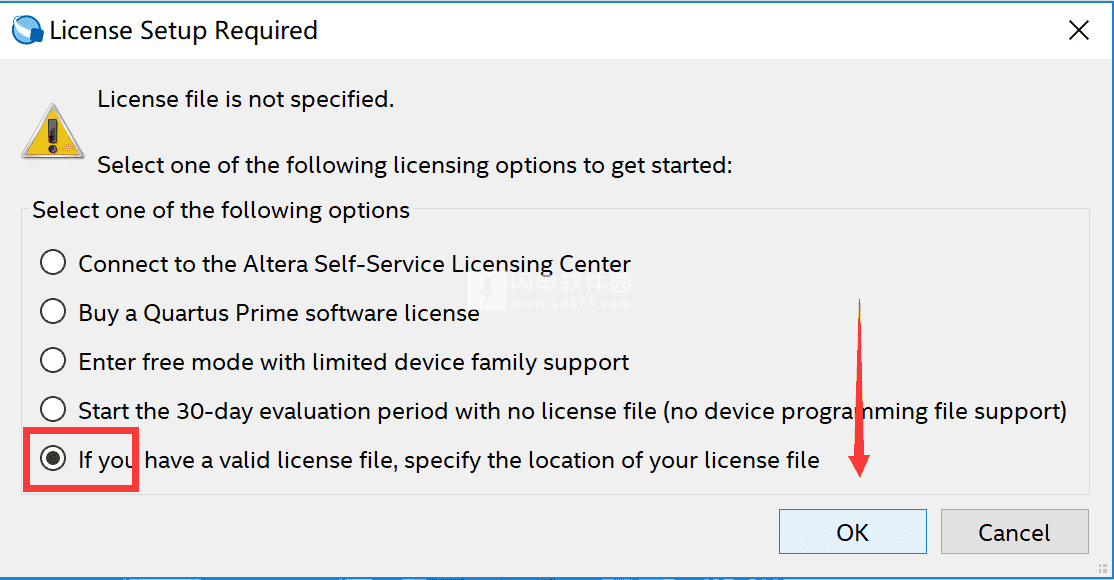

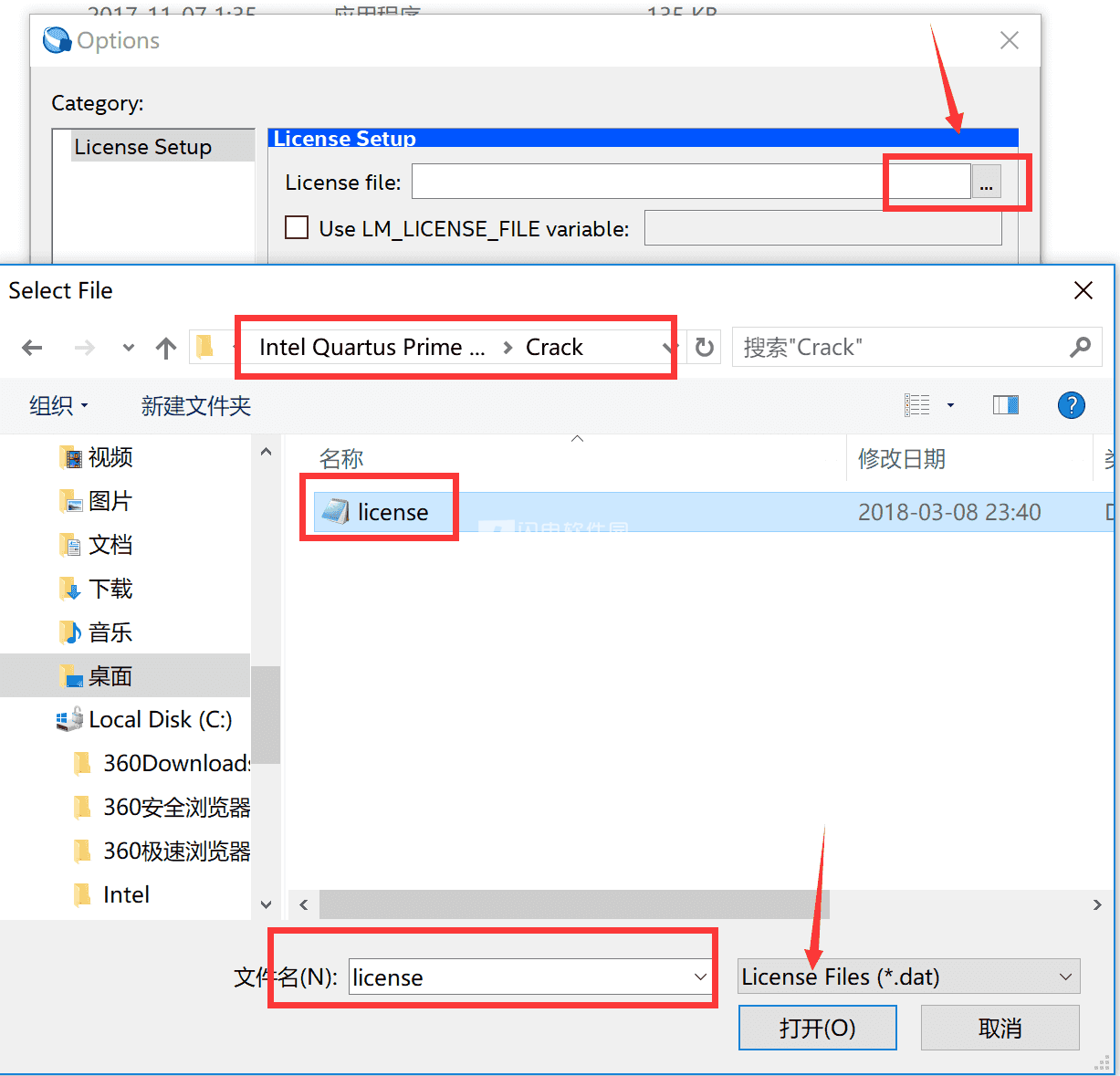

4ЁЂШчЭМЫљЪОЃЌдк“Evaluation Mode”НчУцбЁдёзюКѓвЛЯю“if you hava a valid license file, specify the location of your license file”бЁЯюЃЈШчЙћФњгЕгагааЇЕФаэПЩжЄЮФМўЃЌЧыжИЖЈаэПЩжЄЮФМўЕФЮЛжУЃЉЃЌЕуЛї ok

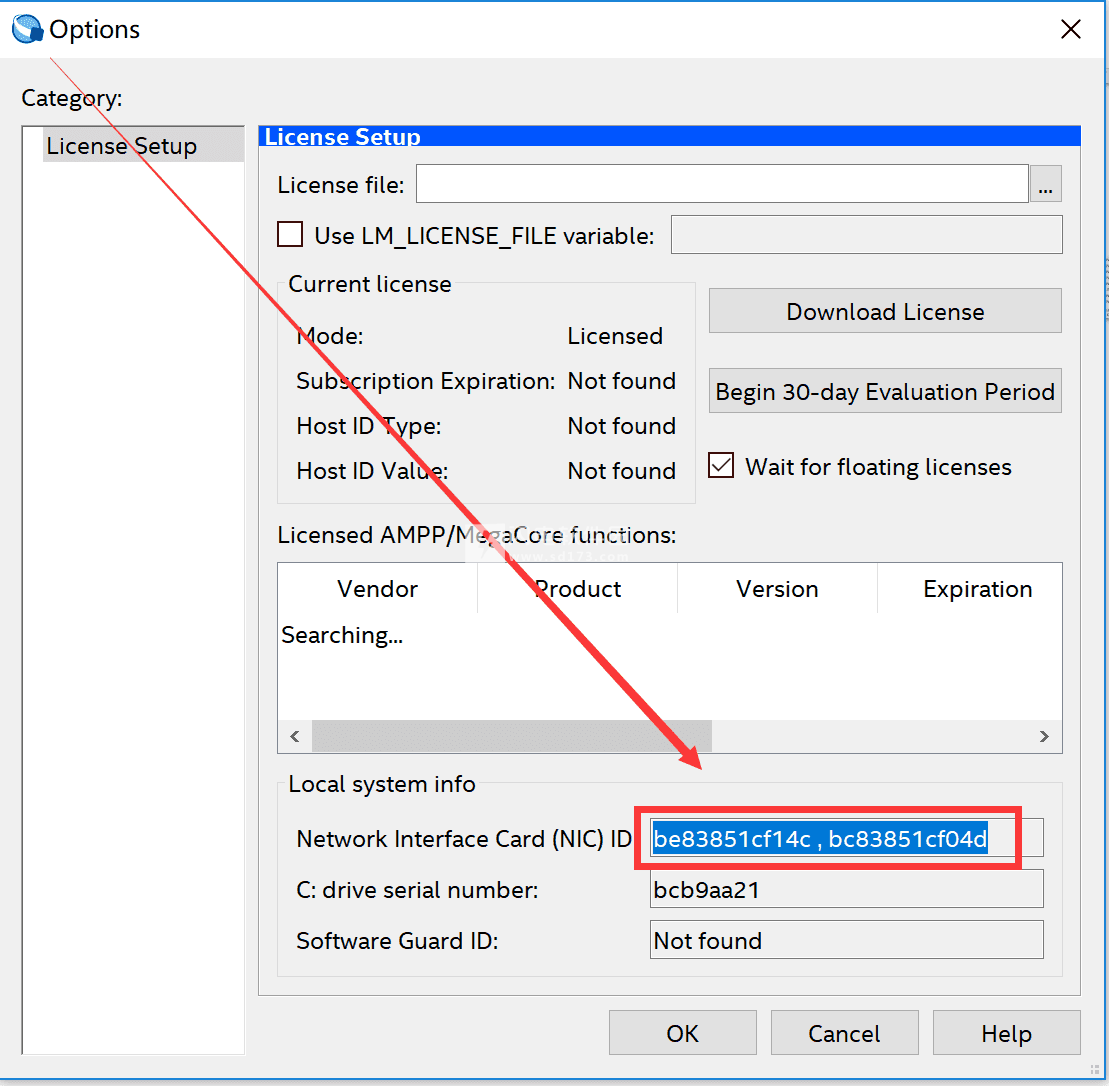

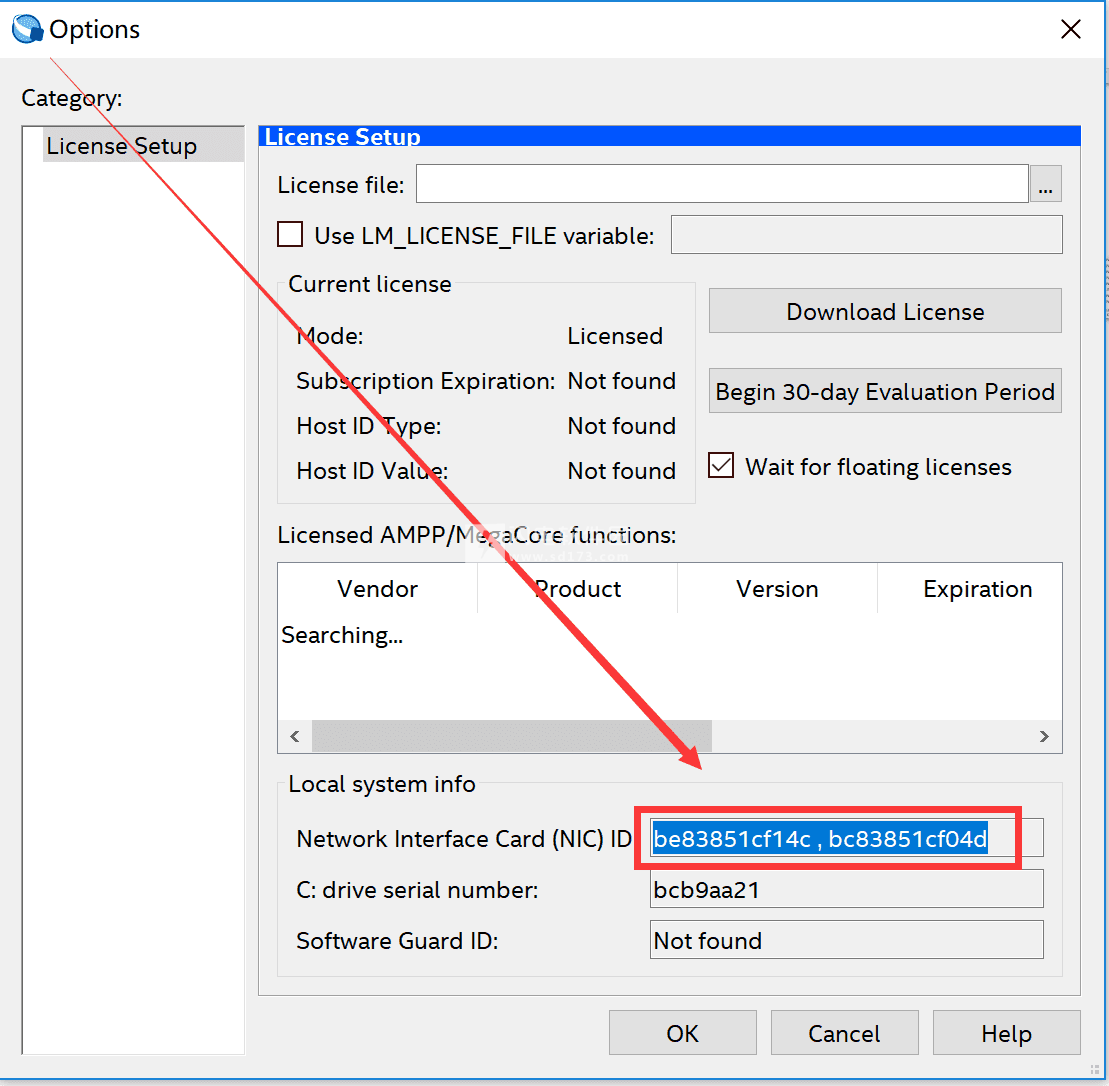

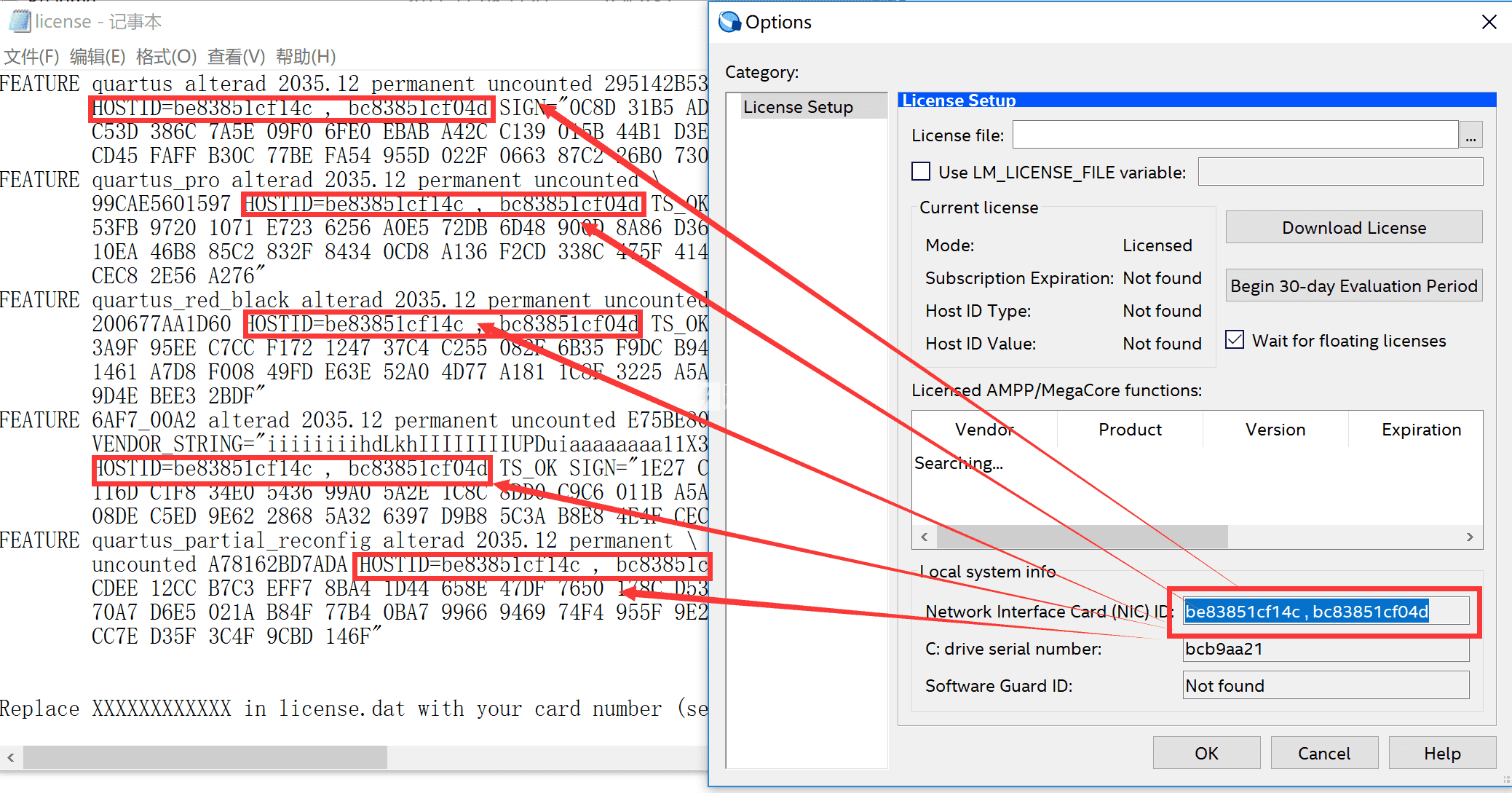

5ЁЂЛёШЁNIC IDЃЌШчЭМ

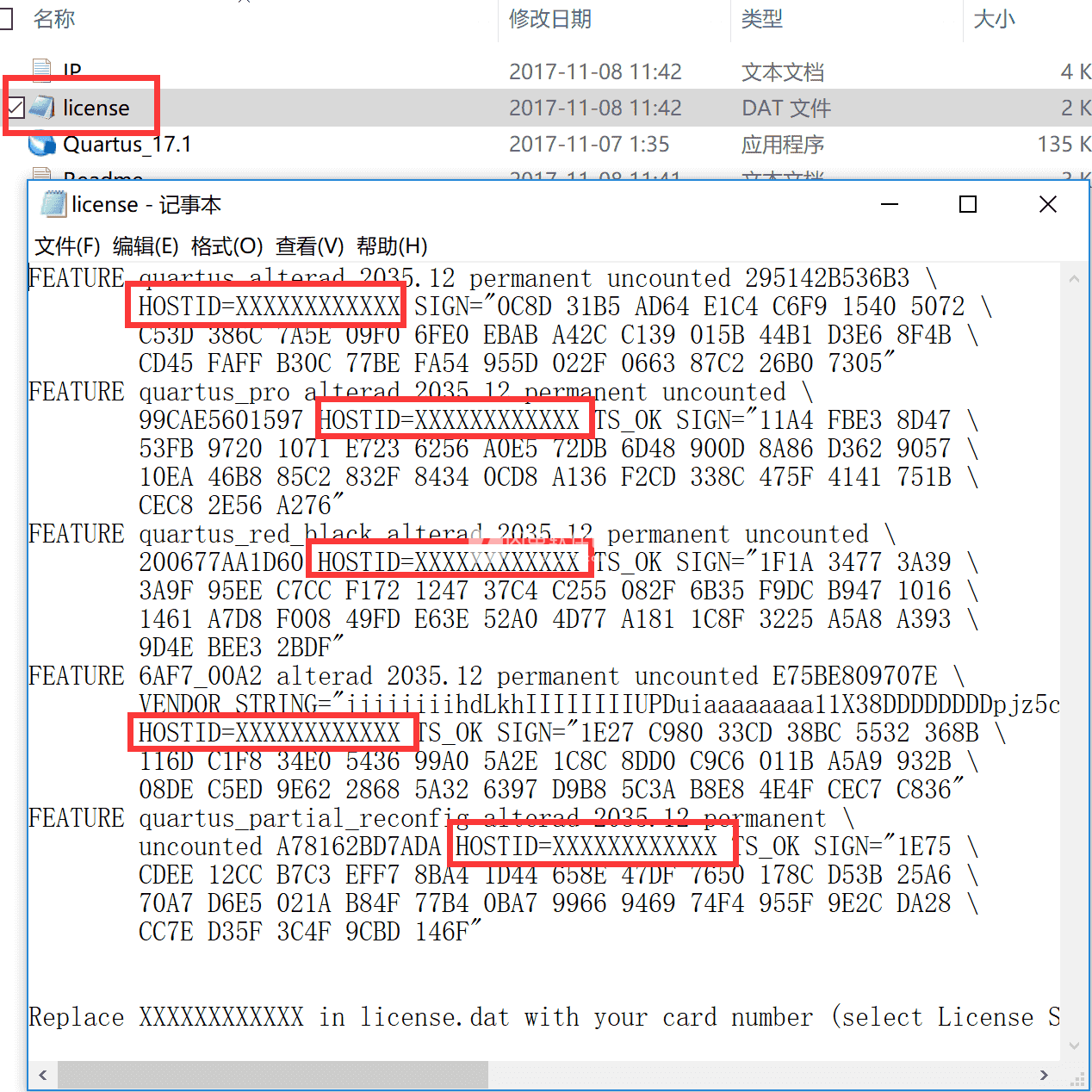

6ЁЂМЧЪТБОЗНЪНДђПЊcrackЮФМўМаФкЕФ“license.dat”ЮФМўЃЌМЧТМКУЮхДІhostid ОпЬхШчЯТЭМКьПђЫљЪО

7.НЋNIC IDИДжЦЕНhostid ШчЭМ

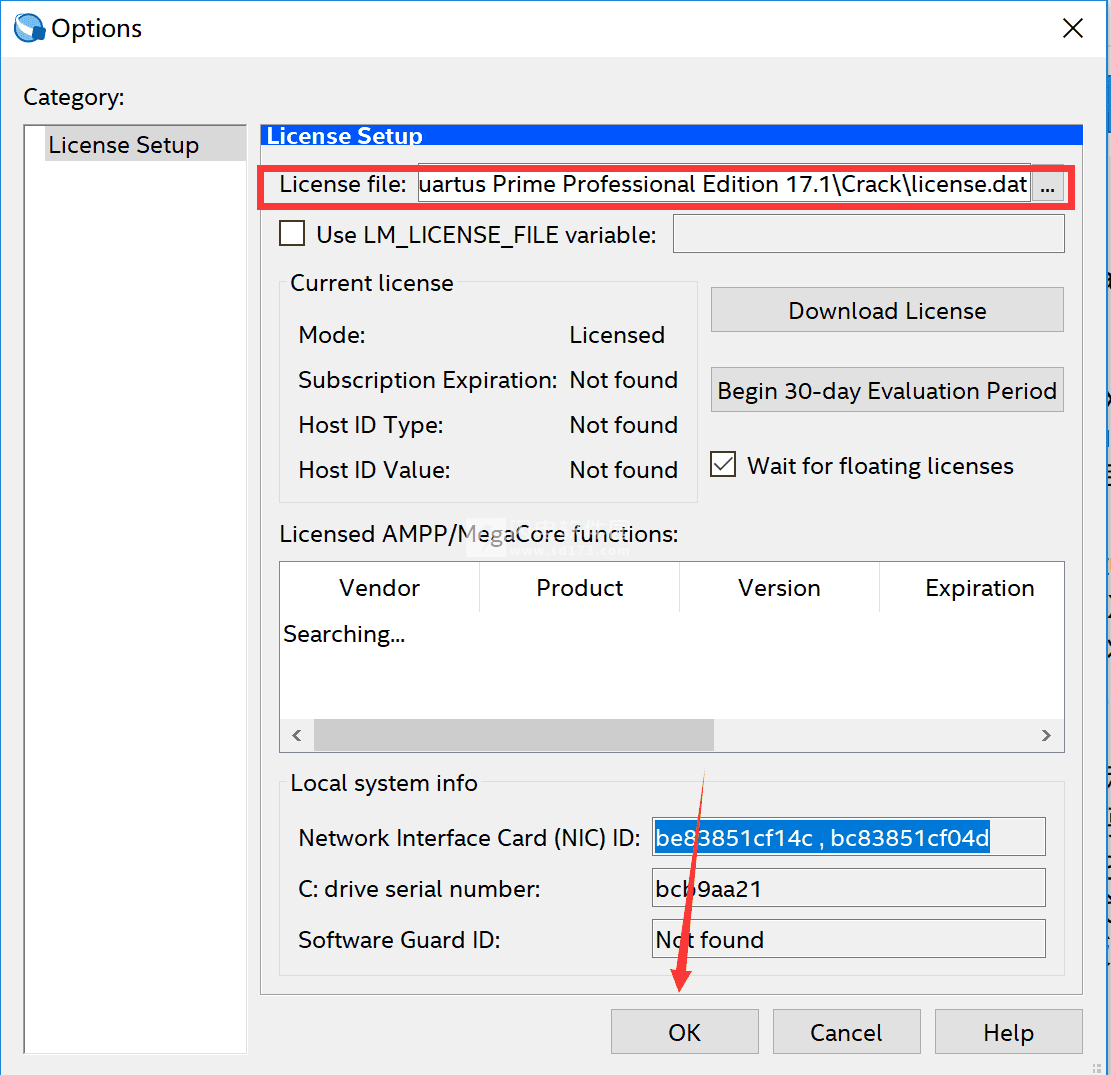

8ЁЂбЁдёаоИФКУЕФ“license.dat”ЮФМўЃЌЕуЛї OK

9.ЦЦНтЭъГЩ

Ш§ЁЂАВзАЦїМўПт

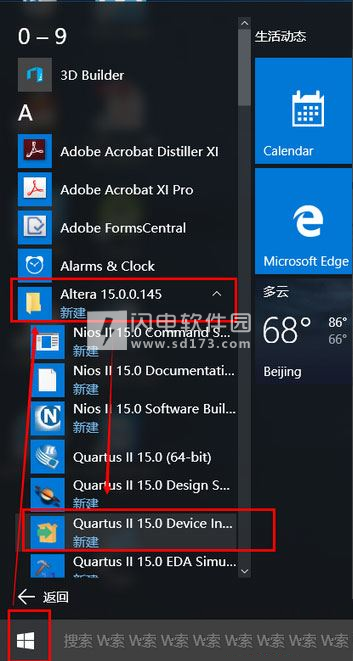

1ЁЂВЮПМQuartus II 15.0ЕФАВзАЃЌдЫаа"ЯЕЭГПЊЗЂВЫЕЅ"->ЫљгагІгУ->Altera 15.0.0.145->Quartus II 15.0 Device Installer

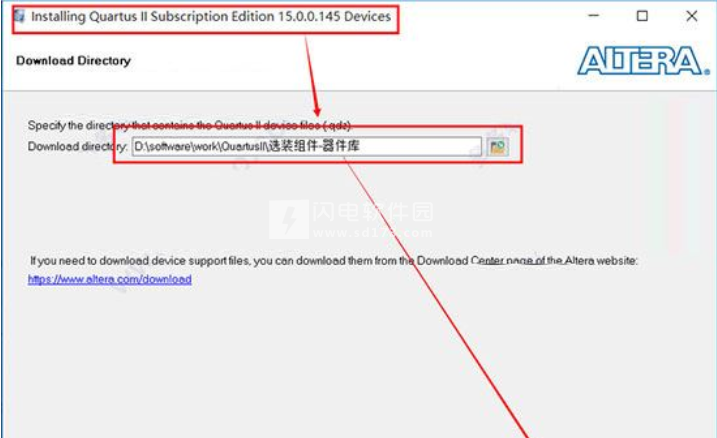

2ЁЂбЁдёИеВХЯТдиЕФЦїМўПтЫљдкЕФФПТМЃЌЕуЛї nextЃЛ

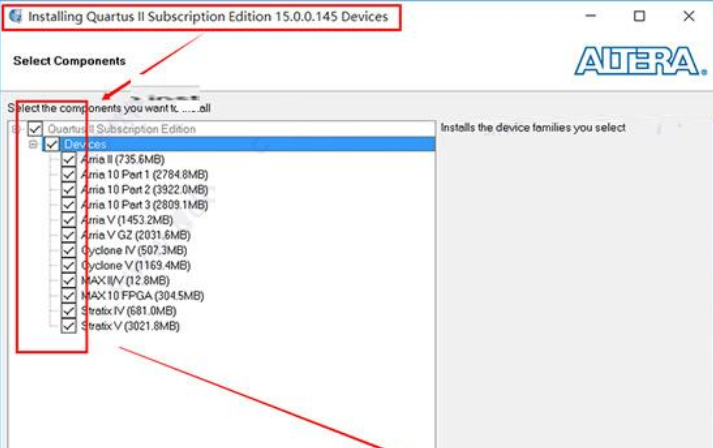

3ЁЂбЁдёЫљгаЕФИДбЁПђЃЌЕуЛїnextБуПЊЪМСЫАВзА

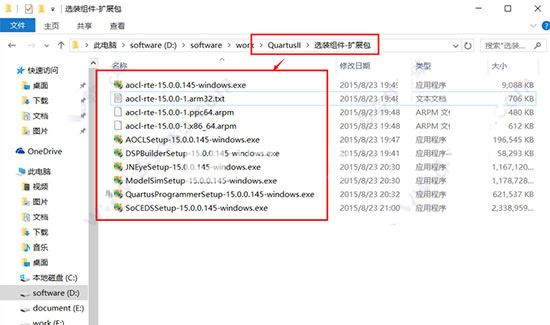

ЫФЁЂАВзАРЉеЙАќ

гЩгкРЉеЙАќжївЊЪЧ exe ПЩжДааГЬађЃЌЫљвдАВзАЦ№РДвВБШНЯЕФМђЕЅ

ШэМўНщЩм

quartus prime 17.1аТЙІФмНщЩм

Quartus

Quartus Prime ШэМў v17.1 гЕгагЂЬиЖћ Quartus Prime зЈвЕАцЕФЫљгааТЬиадКЭаТЙІФмЃЌПЩАяжњФњШЋУцгХЛЏЩшМЦЁЃетвЛШэМўЖдЩшМЦЪІзюЙиаФЕФШ§ИіживЊЗНУцНјааСЫИФНјЃКадФмЁЂЩњВњСІКЭПЩгУадЁЃ

Prime ШэМў v17.1 гЕгагЂЬиЖћ Quartus Prime зЈвЕАцЕФЫљгааТЬиадКЭаТЙІФмЃЌПЩАяжњФњШЋУцгХЛЏЩшМЦЁЃетвЛШэМўЖдЩшМЦЪІзюЙиаФЕФШ§ИіживЊЗНУцНјааСЫИФНјЃКадФмЁЂЩњВњСІКЭПЩгУадЁЃадФм

гЂЬиЖћ Stratix

10 MXЁЂSX КЭ GX ЩшБИжЇГж

10 MXЁЂSX КЭ GX ЩшБИжЇГжгЂЬиЖћ Quartus Prime зЈвЕАцШэМў v17.1 жЇГжгЂЬиЖћ Stratix

10 MXЁЂSX КЭ GX ЩшБИЁЃ

10 MXЁЂSX КЭ GX ЩшБИЁЃгЂЬиЖћ Stratix 10 GX ЩшБИзЈЮЊТњзуИпЭЬЭТСПЯЕЭГЕФИпадФмашЧѓЖјЩшМЦЃЌПЩЬсЙЉИпДя 10 TFLOPS ЕФИЁЕуадФмЃЌЭЌЪБЪеЗЂЦїПЩЮЊаОЦЌФЃПщЁЂаОЦЌЕНаОЦЌКЭБГАхгІгУЬсЙЉИпДя 28.3 Gbps ЕФЫйЖШЃЌЁЃ

Г§СЫгЂЬиЖћ Stratix 10 GX ЩшБИЕФЫљгаЙІФмжЎЭтЃЌгЂЬиЖћ Stratix 10 SX SoC ЛЙгЕгавЛИігВДІРэЦїЯЕЭГЃЌХфБИЪЪгУгкЫљгаУмЖШЕФ 64 ЮЛЫФКЫ ARM* Cortex*-A53 ДІРэЦїЁЃ

гЂЬиЖћ Stratix 10 MX ЩшБИМЏгЂЬиЖћ Stratix 10 FPGA КЭ SoC ЕФПЩБрГЬадКЭСщЛюадгы 3D ЖбЕўИпДјПэФкДц 2 (HBM2) гквЛЩэЁЃгЂЬиЖћ Stratix 10 MX FPGA жЇГж H-tile ЪеЗЂЦїКЭ E-tile ЪеЗЂЦїЁЃ

гЂЬиЖћ Stratix 10 ЩшБИВЩгУСЫДДаТЕФгЂЬиЖћ HyperFlex

FPGA МмЙЙЃЌПЩЬсЙЉБШЩЯвЛДњИпадФм FPGA ИќИпЕФадФмЁЃСЫНтЙигкгЂЬиЖћ HyperFlex FPGA МмЙЙКЭгЂЬиЖћ Stratix 10ЩшБИЕФИќЖраХЯЂЁЃЙлПДStratix 10 бнЪОЪгЦЕвГУцЩЯЫљгазюаТЕФгЂЬиЖћ Stratix 10 FPGA ЪгЦЕЁЃ

FPGA МмЙЙЃЌПЩЬсЙЉБШЩЯвЛДњИпадФм FPGA ИќИпЕФадФмЁЃСЫНтЙигкгЂЬиЖћ HyperFlex FPGA МмЙЙКЭгЂЬиЖћ Stratix 10ЩшБИЕФИќЖраХЯЂЁЃЙлПДStratix 10 бнЪОЪгЦЕвГУцЩЯЫљгазюаТЕФгЂЬиЖћ Stratix 10 FPGA ЪгЦЕЁЃгЂЬиЖћ Quartus Prime ШэМўГЌИажЊЩшМЦСїКЭЪЙгУУцЯђгЂЬиЖћ HyperFlex FPGA МмЙЙЕФПьЫйБрвыЪЧСНУХзюаТЕФХрбЕПЮГЬЃЌПЩАяжњФњСЫНтЙигкгЂЬиЖћ HyperFlex FPGA МмЙЙЕФЯИНкаХЯЂЁЃШчгћСЫНтШчКЮРћгУгЂЬиЖћ HyperFlex FPGA МмЙЙЬиадЃЌЧыЗУЮЪгЂЬиЖћ Quartus Prime ШэМўжЇГжвГУцЃЌЙлПДаТЪгЦЕЁЃ

ЩњВњСІ

гЂЬиЖћ HLS БрвыЦї

НшжњаТЕФгЂЬиЖћ HLS БрвыЦїЃЌФњПЩвдЪЙгУ C++ гябдМгЫй FPGA ПЊЗЂЁЃгЂЬиЖћ HLS БрвыЦїЪЧвЛПюИпМЖКЯГЩ (HLS) ЙЄОпЃЌПЩРћгУВЛЖЈЪБ C++ ЩњГЩеыЖдгЂЬиЖћ FPGA гХЛЏЕФЩњВњжЪСПМФДцЦїДЋЪфМЖ (RTL) ЩшМЦЁЃШчгћСЫНтИќЖрЯъЯИаХЯЂЃЌЧыЗУЮЪгЂЬиЖћ HLS БрвыЦїЭјвГЁЃЧызЂвтЃЌгЂЬиЖћ HLS БрвыЦїжЇГжЫљгаАцБОЕФгЂЬиЖћ Quartus Prime ШэМў v17.1ЁЃ

ИФНјЛљгкПщЕФЩшМЦСї

гЂЬиЖћ Stratix 10ЁЂгЂЬиЖћ Arria

10 КЭгЂЬиЖћ Cyclone

10 КЭгЂЬиЖћ Cyclone 10 ЩшБИВњЦЗМвзхЯждкжЇГжЛљгкПщЕФЩшМЦСїЃЌАќРЈЩшМЦПщжигУКЭЛљгкдіСППщЕФБрвыЁЃгЂЬиЖћ Quartus Prime зЈвЕАцЪжВсЕк 1 ОэЕФЛљгкПщЕФЩшМЦСїВПЗжНщЩмСЫетаЉЩшМЦСїЕФаТЬиадЁЃ

10 ЩшБИВњЦЗМвзхЯждкжЇГжЛљгкПщЕФЩшМЦСїЃЌАќРЈЩшМЦПщжигУКЭЛљгкдіСППщЕФБрвыЁЃгЂЬиЖћ Quartus Prime зЈвЕАцЪжВсЕк 1 ОэЕФЛљгкПщЕФЩшМЦСїВПЗжНщЩмСЫетаЉЩшМЦСїЕФаТЬиадЁЃ ВПЗжжиХфжУ

ВПЗжжиХфжУжЇГжФњЖЏЬЌжиаТХфжУ FPGA ЕФвЛВПЗжЃЌЭЌЪБШУЪЃгрЕФ FPGA ЩшМЦМЬајдЫааЁЃгЂЬиЖћ Quartus Prime зЈвЕАцШэМў v17.1 жагаШ§ИіУцЯђгЂЬиЖћ Stratix 10 КЭгЂЬиЖћ Arria 10 ЩшБИВњЦЗМвзхЕФживЊВПЗжжиХфжУЙІФмЃК

ЗжВуВПЗжжиХфжУ

ФЃФтВПЗжжиХфжУ

ЭЈЙ§ Signal Tap ТпМЗжЮіЦїЭЌВНЕїЪдОВЬЌКЭЖЏЬЌВПЗжжиХфжУЧјгђ

ШчгћСЫНтгаЙиетаЉЬиадЕФИќЖраХЯЂЃЌЧыЗУЮЪВПЗжжиХфжУвГУцЁЃ

ТпМЕШМлМьВщ

ТпМЕШМлМьВщ (LEC) ЪЧвЛЯюаТЬиадЃЌгЩгЂЬиЖћ Quartus Prime зЈвЕАцШэМў v17.1 жаЕФгЂЬиЖћ HyperFlex FPGA МмЙЙжиЖЈЪБЬсЙЉжЇГжЁЃЫќжЄУїЃЌОЙ§гЂЬиЖћ HyperFlex FPGA МмЙЙгХЛЏКѓЕФЭјБэЯрЕБгкЪЪХфКѓЭјБэЁЃгаЙиЕкШ§ЗНЙЄОпЃЌЧыВЮдФ OneSpin МАЦф 360-EC FPGA НтОіЗНАИЁЃ

Platform DesignerЃЈжЎЧАУћЮЊ QsysЃЉ

НшжњгЂЬиЖћ Quartus Prime зЈвЕАцШэМў v17.1ЃЌФњПЩвдНЋ C++ (.cpp) ЮФМўЬэМгжС Platform DesignerЃЌВЂЮЇШЦЫќУЧЖЈвхжЊЪЖВњШЈ (IP) зщМўЁЃФњЛЙПЩвдНЋЪЙгУ SystemVerilog НгПкЕФ IP зщМўВЂШыЕН Platform Designer ЯЕЭГжаЁЃгаЙиЫљгаетаЉЬиадЕФИќЖрЯъЯИаХЯЂЃЌЧыВЮМћгЂЬиЖћ Quartus Prime зЈвЕАцЪжВсЕк 1 ОэКЭPlatform DesignerЃЈжЎЧАУћЮЊ QsysЃЉЭјвГЩЯЕФдк Qsys Pro жаДДНЈЯЕЭГВПЗжЁЃ

гЂЬиЖћ Stratix 10 ЩшБИ Post-Fit Tap АяжњМгПьЕїЪдЕќДњ

гЂЬиЖћ Stratix 10 FPGA ЩшМЦЯждкПЩвдЮоашжиаТБрвыБуПЩИќИФ Signal Tap ТпМЗжЮівЧЬНВтЕуЃЌДгЖјМгПьЕїЪдЕќДњЁЃвђДЫЃЌШчЙћЩшМЦжажЛгаЬНВтЕуЗЂЩњБфЛЏЃЌдђЮоашжиаТБрвыЩшМЦЃЌжЛашВМжУЬНВтЕуМДПЩЃЌДгЖјНкЪЁДѓСПЪБМфЁЃШчгћСЫНтИќЖраХЯЂЃЌЧыдФЖСгЂЬиЖћ Quartus Prime зЈвЕАцЪжВсЕк 3 ОэЕФЪЙгУ Signal Tap ТпМЗжЮіЦїЕїЪдЩшМЦВПЗжЁЃ

Design Partition Planner

гЂЬиЖћ Quartus Prime зЈвЕАцШэМў v17.1 жаЕФ Design Partition Planner дЪаэФњВщПДЩшМЦСЌНгКЭВуДЮНсЙЙЃЌВЂАяжњФњДДНЈКЭгХЛЏЩшМЦЗжЧјВЂЦРЙРЦфжЪСПЁЃШчгћСЫНтИќЖраХЯЂЃЌЧыВЮМћгЂЬиЖћ Quartus Prime зЈвЕАцЪжВсЕк 1 ОэЕФЩшМЦЗжЧјжИФЯВПЗжЁЃ

ПЩгУад

дЦЖЫЕФШэМўЙЄОп

НшжњгЂЬиЖћ Quartus Prime зЈвЕАцШэМў v17.1ЃЌФњПЩвдЪЙгУдЦЖЫЕФгЂЬиЖћ FPGA БрГЬЙЄОпМгЫйгІгУЃЌдк Nimbix ЬсЙЉЕФИпадФмМЦЫуЛЗОГжаЖд FPGA НјааБрГЬЁЃШчгћСЫНтИќЖраХЯЂЃЌЧыВЮМћдЦЗўЮёЭјвГЁЃ

ПЩгУаддіЧП

гЂЬиЖћ Quartus Prime зЈвЕАцШэМў v17.1 жаЕФвЛаЉЬиадЯждкДгПЩгУадЗНУцНјааСЫдіЧПЁЃЦфжавЛаЉЬиадШчЯТЃК

жиаТЩшМЦЕФ IP Щ§МЖЖдЛАПђ

ТпМЫјЖЈЧјгђЁЃЮвУЧЮЊФњЬсЙЉСЫвЛУХChip Planner ХрбЕПЮГЬЃЌПЩАяжњФњСЫНтВМОжЙцЛЎКЭТпМЫјЖЈЧјгђЁЃ

ЙІФмЬиЩЋ

Quartus IIЬсЙЉСЫЭъШЋМЏГЩЧвгыЕчТЗНсЙЙЮоЙиЕФПЊЗЂАќЛЗОГЃЌОпгаЪ§зжТпМЩшМЦЕФШЋВПЬиадЃЌАќРЈЃК

1ЁЂПЩРћгУдРэЭМЁЂНсЙЙПђЭМЁЂVerilogHDLЁЂAHDLКЭVHDLЭъГЩЕчТЗУшЪіЃЌВЂНЋЦфБЃДцЮЊЩшМЦЪЕЬхЮФМў;

2ЁЂаОЦЌ(ЕчТЗ)ЦНУцВМОжСЌЯпБрМ;

3ЁЂLogicLockдіСПЩшМЦЗНЗЈЃЌгУЛЇПЩНЈСЂВЂгХЛЏЯЕЭГЃЌШЛКѓЬэМгЖддЪМЯЕЭГЕФадФмгАЯьНЯаЁЛђЮогАЯьЕФКѓајФЃПщ;

4ЁЂЙІФмЧПДѓЕФТпМзлКЯЙЄОп;

5ЁЂЭъБИЕФЕчТЗЙІФмЗТецгыЪБађТпМЗТецЙЄОп;ЖЈЪБ/ЪБађЗжЮігыЙиМќТЗОЖбгЪБЗжЮі;ПЩЪЙгУSignalTap IIТпМЗжЮіЙЄОпНјааЧЖШыЪНЕФТпМЗжЮі;

6ЁЂжЇГжШэМўдДЮФМўЕФЬэМгКЭДДНЈЃЌВЂНЋЫќУЧСДНгЦ№РДЩњГЩБрГЬЮФМў;

7ЁЂЪЙгУзщКЯБрвыЗНЪНПЩвЛДЮЭъГЩећЬхЩшМЦСїГЬ;

8ЁЂздЖЏЖЈЮЛБрвыДэЮѓ;

9ЁЂИпаЇЕФЦкМфБрГЬгыбщжЄЙЄОп;

10ЁЂПЩЖСШыБъзМЕФEDIFЭјБэЮФМўЁЂVHDLЭјБэЮФМўКЭVerilogЭјБэЮФМў;

11ЁЂФмЩњГЩЕкШ§ЗНEDAШэМўЪЙгУЕФVHDLЭјБэЮФМўКЭVerilogЭјБэЮФМўЁЃ

БОЬћГЄЦкИќаТзюаТАц ЧыЪеВиЯТдиЃЁАцШЈЩљУїЃКБОеОЬсЕФађСаКХЁЂзЂВсТыЁЂзЂВсЛњЁЂЦЦНтВЙЖЁЕШОљРДздЛЅСЊЭјЃЌНіЙЉбЇЯАНЛСїжЎгУЃЌЧыдкЯТдиКѓ24аЁЪБФкЩОГ§ЁЃ