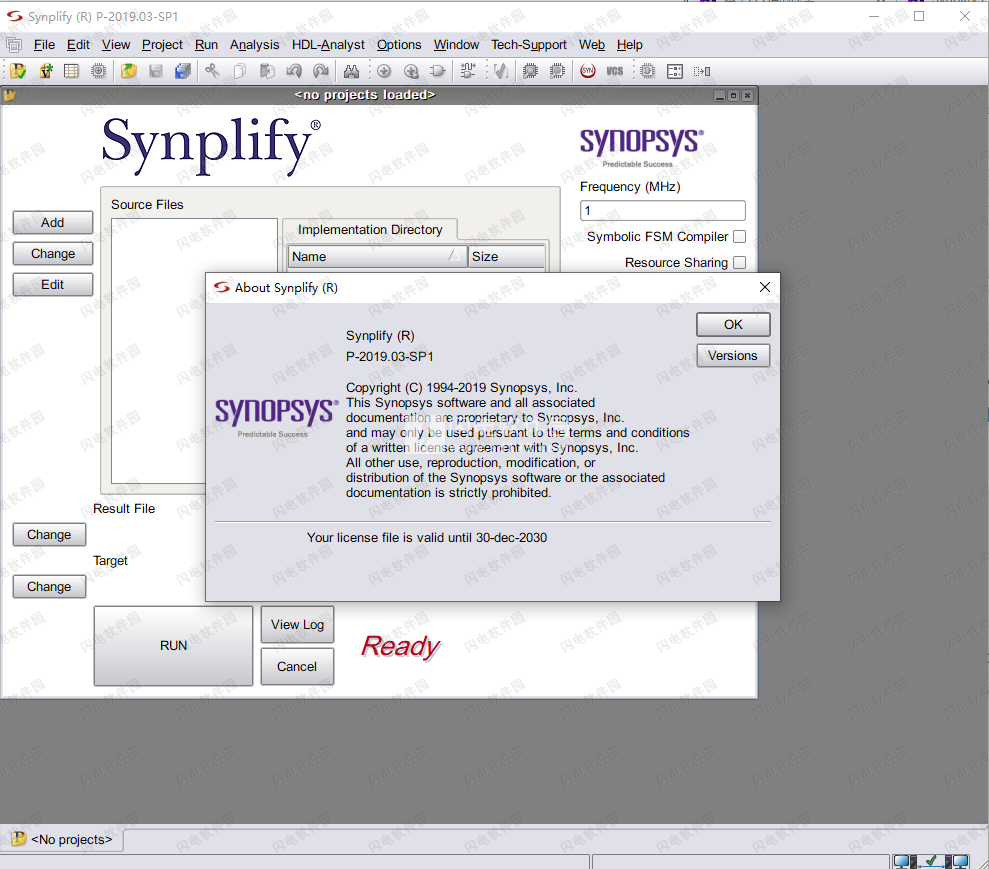

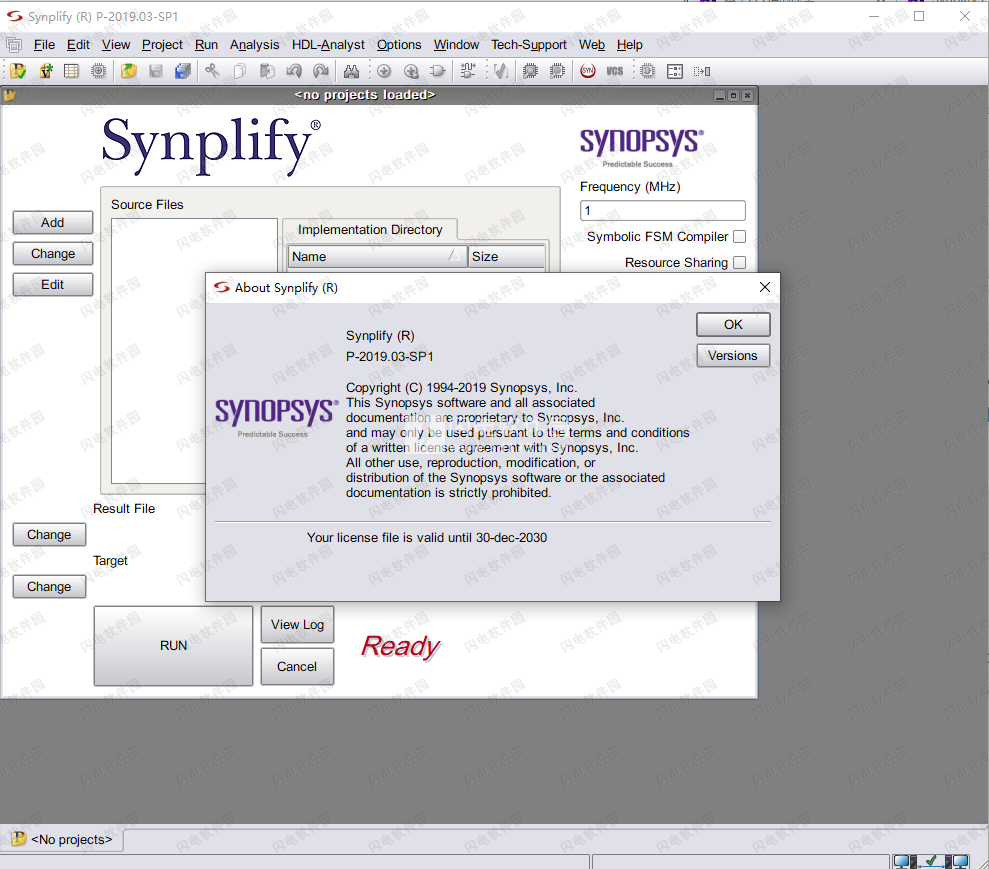

软件标签:Synopsys FPGA P-2019

Synopsys FPGA P-2019是提供了完整的解决方案,本产品套件可帮助用户更好的进行电路的设计和编程,用户友好的原型开发工具,可直接从RTL源代码和ASIC IP中使用。提供从计划到综合的集成FPGA设计流程,提供用于高级FPGA和基于FPGA的原型的快速,可靠的逻辑综合解决方案,可自动采用多种成熟的方法来减轻软错误,例如单事件翻转(SEU),这些问题在最新的FPGA工艺几何中越来越多地出现以及提供类似于FPGA硬件操作的可视性!由于每个过程节点的容量增加和功率降低,可编程芯片的使用越来越多。设计师现在正面临一些严峻的新挑战。例如,28nm FPGA具有相当于5000万个ASIC门的容量,这推动了对功能更强大的综合工具的需求。Synplify综合工具为设计人员提供了可提供自动化,更快的周转时间,更可预测的时序收敛,高可靠性设计,电源管理,先进的验证技术以及许多来源的IP集成的方法。Synplify工具集可自动执行许多功能,因此设计人员可以专注于自己的产品差异化,同时满足进度和成本目标。破解版本下载,含安装激活教程,欢迎有需要的朋友来本站下载体验!

功能特色

一、Synplify Pro

FPGA设计的逻辑综合

SynplifyPro®FPGA综合软件是用于生产高性能和高性价比FPGA设计的行业标准。Synplify软件支持最新的VHDL和Verilog语言结构,包括SystemVerilog和VHDL-2008。该软件还支持来自多个FPGA供应商的FPGA体系结构,包括Altera,Achronix,Lattice,Microsemi和Xilinx,它们均来自单个RTL和约束源。Synplify Pro软件使用单个易于使用的界面,并能够执行增量综合和直观的HDL代码分析。

对于需要尽可能快的综合运行时间和最高质量的时序,面积和功耗结果的大型设计的设计人员。Synplify®Premier软件提供了Synplify Pro的所有功能以及一整套用于高级FPGA设计的工具

1、增量,基于块的和自下而上的流程,从一次运行到下一次运行可获得一致的结果

2、自动编译点增量流可将运行时间提高多达4倍,同时保持QoR

3、加速运行时间,最多支持4个处理器

4、脚本和Tcl/Find支持流程自动化以及可自定义的综合,调试和报告功能

5、使用Achronix,Altera,Lattice,Microsemi,Xilinx的FPGA获得最佳面积和时序结果

6、分层团队设计流程,允许并行和/或地理分布的设计开发

7、全面的语言支持,包括Verilog,VHDL,SystemVerilog,VHDL-2008和混合语言设计

8、FSM编译器和FSM Explorer,用于从RTL自动提取和优化有限状态机

9、图形状态机查看器可自动创建气泡图以调试和记录FSM

10、自动存储器和DSP推理可自动实现设计,并具有最佳的面积,功耗和时序质量

11、用于分析的增量静态时序允许更新时序异常约束,并可以立即查看结果,而无需重新合成

12、HDL Analyst交互式图形分析和调试工具,用于设计诊断,问题隔离以及功能和性能分析

二、Synplify Premier

加快FPGA设计和基于FPGA的原型的实现

SynplifyPremier®是业界最先进的FPGA设计和调试环境。Synplify综合工具提供了快速的运行时间,性能,用于成本和功耗降低的区域优化,多FPGA供应商支持,增量和团队设计功能,以加快FPGA设计开发的速度。Synplify Premier包含的功能可自动创建高度可靠的设计,例如用于医疗,汽车,工业自动化,通信,军事和航空航天应用的设计。

Premier包含Identify Instrumentor,以提供一种易于使用的方法来查找在板上运行的FPGA设计中的功能错误。该解决方案为模拟器提供了对已实现的FPGA硬件的可视性,并查看了直接叠加在RTL代码上的运行中的FPGA的实际信号值。这样,用户可以以目标操作速度执行系统内调试。

Premier旨在接受优化的RTL,第三方和内部/先前开发的IP,从而可以进行广泛的设计探索和更快的实施。

此外,Synplify集成了对DesignWare®IP,Identify RTL Debugger,VCS®高性能功能验证的支持,以及与ASIC兼容的综合流程,可用于创建基于FPGA的原型。

1、自动门控时钟转换,支持基于FPGA的原型设计

2、集成的Identify RTL调试器,可快速发现功能错误

3、自动化设计实现了高可靠性和安全性至关重要的设计,包括DO-254,ISO 26262和IEC 61508

4、与VCS Simulator集成并直接支持DesignWare IP

5、时序性能和面积/成本降低的最佳结果质量(QoR)

6、分布式综合,支持单机或多机综合

7、加速的运行时提供多达3倍的运行时,每个许可证最多支持4个处理器

8、自动存储器和DSP推理可提供最佳的区域,功率和时序质量

9、支持VHDL,Verilog,SystemVerilog,VHDL-2008和混合语言综合的广泛语言

10、通过HDL Analyst和分层调试流程进行高级设计调试和诊断

闪电小编说明:

Synopsys的 基于FPGA的原型开发解决方案 缩短了产品上市时间,并通过支持早期嵌入式软件开发并允许在芯片制造之前就进行软硬件协同设计,从而避免了昂贵的设备重新设计。除了完全集成的,基于FPGA的原型开发解决方案之外,Synopsys还为基于FPGA的原型开发人员提供了一套工具,以构建自己的开发板,Synplify Premier为ASIC和SoC设计人员提供了多种功能,有助于加速半导体原型的开发。设计人员面临的首要挑战之一是更换设计中非基于FPGA的部分,例如存储器,时钟配置和ASIC测试电路。Synplify Premier除了解析多种语言格式和约束文件外,还提供了一种用于处理辅助文件的简便方法。下一个挑战是第三方,Synopsys和内部开发的IP的导入和处理,Synplify Premier可以实现自动化以大大提高生产率。最后,Synplify Premier使时钟转换自动化,从而使ASIC设计适合FPGA的时钟结构。

软件无法下载?不知道解压密码?微信关注订阅号"闪电下载"获取

本帖长期更新最新版 请收藏下载!版权声明:本站提的序列号、注册码、注册机、破解补丁等均来自互联网,仅供学习交流之用,请在下载后24小时内删除。